Verification has become the dominant bottleneck in modern chip design. As much as 70% of the overall design cycle is now spent on verification, a figure driven upward by increasing design complexity, compressed schedules, and a chronic shortage of design verification (DV) engineering bandwidth. Modern chips generate thousands… Read More

Tag: CPUs

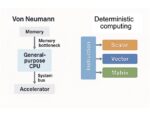

Beyond Von Neumann: Toward a Unified Deterministic Architecture

By Thang Tran

For more than half a century, the foundations of computing have stood on a single architecture: the Von Neumann or Harvard model. Nearly all modern chips—CPUs, GPUs, and even many specialized accelerators—rely on some variant of this design. Over time, the industry has layered on complexity and specialization to… Read More