Questions: Whatever happened to the IFS separation.

Separate board

They should have a separate CEO

Separate finances?

There are some huge tradeoffs coming between product and foundry and they are not behaving independently. Have they announced they are not really independent.

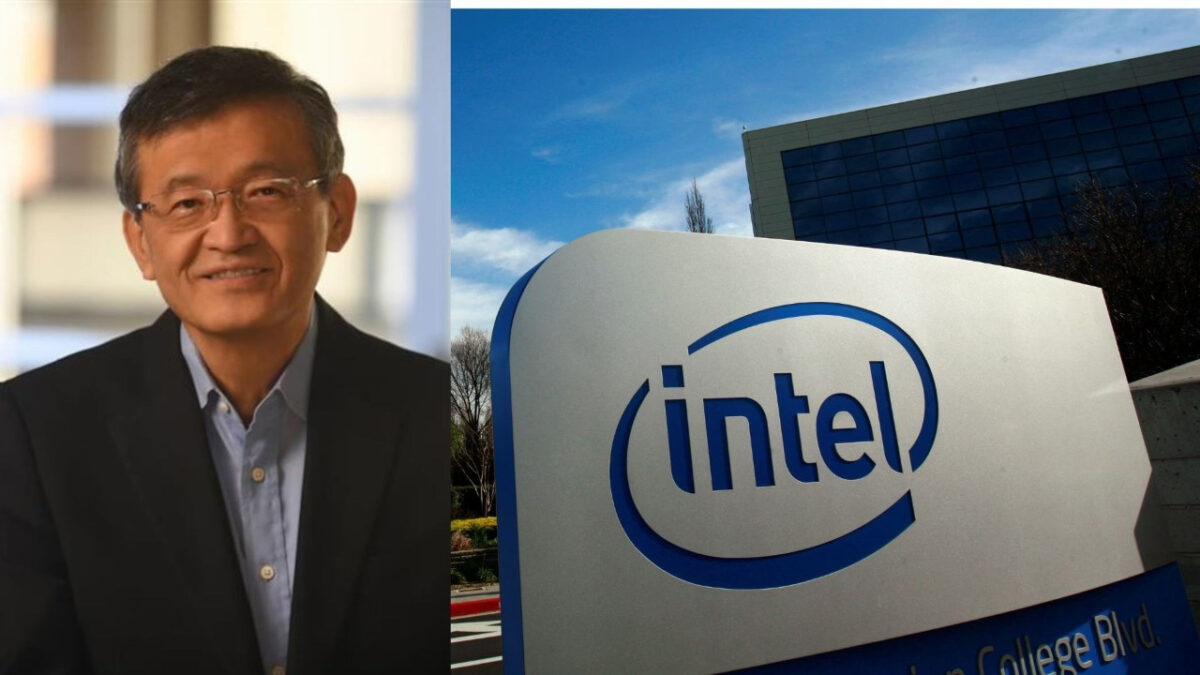

I have not heard a word about it since Lib-Bu took the CEO job. I really do think Lip-Bu is looking to maximize Intel shareholder value. Why else would Softbank and Nvidia invest $7B?

It seems to me that would best be done when IFS is successful enough to be sold or go IPO. I'm not a finance person so this is above my paygrade but I did hear it discussed by people who would know.

When IFS starts talking about big 18A and 14A customers spinning it out will be much more viable. If IFS does not get big 18A and 14A customers it would be a moot point.