Summary

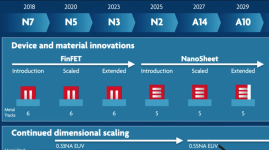

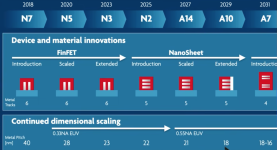

-On the left: Starting from Finfet, next is "Nanosheet"

-Lithography: From 0.33NA EUV to 0.55NA EUV starting at the second Nanosheet generation ("Scaled")

-Metal pitch: In 2025, we're at 22nm in the first generation Nanosheet. This is down from 23nm at the last Finfet node, N3. The next scaling step will take us to 21nm.

-Metal pitch, backside: The pitch is relaxed considerably on the backside wiring. Initially 160-65nm, then in the second Nanosheet generation, 115-45nm.

-Ian Cutressdescribes the last Nanosheet generation as "Forksheet". That takes us to 18nm metal pitch with A10 designation.

-This brings us to the 2031 timeframe with a new transistor: CFET ("Complementary Fet"). This stacks the GAA NMOS and PMOS transistors on top of each other, doubling density. The designation is A7.

-Ian describes the brick wall CFETs need to climb. Up to CFET, the high temperature processing used to form the transistor is done once. At CFET, it will need to be done twice. This is not a lithography challenge. It's a temperature-resistant materials challenge. And as we've found with batteries, it can be slow progress when it comes to materials. 2031 is not far off, and breakthroughs are needed.

-Assuming everything goes well with CFETs, we then move to 2DFET. This is a CFET with a single layer of a material like (Ian suggests) aluminum disulfide, tungsten ditelluride, or tungsten diselenide, a family of materials that naturally form monolayers. They grow at high temperatures which is a red brick. Junction resistance is a red brick. How to dope 2D materials is a red brick.

-Another big advance will be needed to get there: 0.75NA EUV.