HONG KONG — June 6, 2025 — Easy-Logic proudly introduces a groundbreaking stage-based ECO design environment, built into the EasylogicECO tool, to meet the rapidly evolving functional ECO (Engineering Change Order) demands of today’s ASIC design industry.

These stage-based flows simplify functional ECO operations through built-in modules that address both functionality changes and alignment with the user’s ASIC design flow. With the inclusion of these new features, EasylogicECO has demonstrated a reduction in ECO turnaround time by more than 50% compared to traditional approaches.

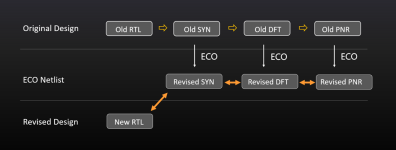

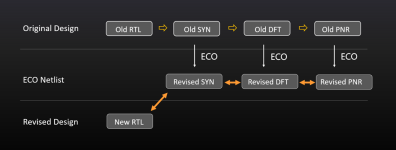

Dr. Sean Wei, CEO of Easy-Logic Technology, emphasizes the importance of this new offering: “In any functional ECO scenario, designers face a layered challenge. First comes the complexity of implementing logic changes. Then, each design stage—synthesis, DFT, floorplanning, and place-and-route—requires its own variation of the ECO logic. Finally, every change must be verified before the flow can advance. These challenges accumulate quickly, threatening both the schedule and silicon quality.

By offering flexibility, speed, and deep flow integration, EasylogicECO turns ECO into a manageable, streamlined part of the ASIC design lifecycle — empowering teams to respond quickly to change without compromising quality or design intent.”

Figure 1: An example of the layered challenge in an ECO operation

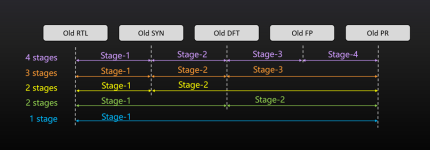

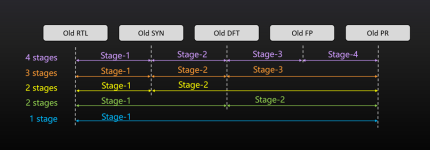

With a stage-aware architecture designed to align with the user’s ASIC design process, EasylogicECO provides five built-in functional ECO flows, each designed to mirror a common ASIC flow scenario. Each stage in the ECO flow consists of an operation module with embedded functionality and configurable switches, and all modules in the same design flow are tightly integrated. This allows users to further control their ECO results based on specific application needs.

Figure 2: Stage-based ECO design modules built-in into EasylogicECO

From an application perspective, each built-in flow reflects a typical ASIC design flow scenario. Examples include:

• 1-stage ECO flow (Blue): Ideal for small digital circuitry, such as mixed-signal ASIC designs. This flow supports fast-turnaround environments where ECO requests occur frequently but remain localized, and ECO windows are short.

• 2-stage ECO flow (Green): Designed for streamlined handoffs between traditional front-end and back-end design teams, where the front-end covers RTL design, synthesis, and DFT phases.

• 2-stage ECO flow (Yellow): This second variant of the two-stage flow supports designs that require an RTL handoff to the implementation team during the design process.

• 3-stage ECO flow (Orange): Perfect for very large-scale digital ASICs, such as mobile application processors or network switches. This flow targets a well-defined ECO process involving separate RTL design and DFT teams, as well as back-end implementation. Result verification is performed at the synthesis and DFT stages before committing back-end changes to minimize risk.

• 4-stage ECO flow (Purple): Tailored for ultra-large ASIC designs such as GPUs or AI server chips, this flow excels in environments where the chip comprises many replicated or hierarchical blocks. It includes a floorplanning step to adjust the patch logic before place and route (P&R) using physical guidance — particularly when the distance between blocks impacts patch timing.

Easy-Logic will showcase its new functional ECO environment at DAC 2025, taking place June 22–25 in San Francisco (Booth # 2521). Visitors are encouraged to schedule detailed discussions in advance to explore how EasylogicECO can be seamlessly integrated into their design environments. To get in touch, please use our Contact Us form at https://www.easylogiceda.com/en/contact.html.

About Easy-Logic Technology

Easy-Logic Technology is a leading provider of cutting-edge functional ECO solutions in the semiconductor industry. With a focus on innovation and customer satisfaction, Easy-Logic Technology delivers advanced tools and technologies that enable its customers to achieve excellence in ASIC design.

Media Contact:

Jimmy Chen

Product Marketing Director

Easy-Logic Technology Limited

Phone: (408)718-2978

Email: jimmy@easylogiceda.com

Website: www.easylogiceda.com/en

Link to Press Release

These stage-based flows simplify functional ECO operations through built-in modules that address both functionality changes and alignment with the user’s ASIC design flow. With the inclusion of these new features, EasylogicECO has demonstrated a reduction in ECO turnaround time by more than 50% compared to traditional approaches.

Dr. Sean Wei, CEO of Easy-Logic Technology, emphasizes the importance of this new offering: “In any functional ECO scenario, designers face a layered challenge. First comes the complexity of implementing logic changes. Then, each design stage—synthesis, DFT, floorplanning, and place-and-route—requires its own variation of the ECO logic. Finally, every change must be verified before the flow can advance. These challenges accumulate quickly, threatening both the schedule and silicon quality.

By offering flexibility, speed, and deep flow integration, EasylogicECO turns ECO into a manageable, streamlined part of the ASIC design lifecycle — empowering teams to respond quickly to change without compromising quality or design intent.”

Figure 1: An example of the layered challenge in an ECO operation

With a stage-aware architecture designed to align with the user’s ASIC design process, EasylogicECO provides five built-in functional ECO flows, each designed to mirror a common ASIC flow scenario. Each stage in the ECO flow consists of an operation module with embedded functionality and configurable switches, and all modules in the same design flow are tightly integrated. This allows users to further control their ECO results based on specific application needs.

Figure 2: Stage-based ECO design modules built-in into EasylogicECO

From an application perspective, each built-in flow reflects a typical ASIC design flow scenario. Examples include:

• 1-stage ECO flow (Blue): Ideal for small digital circuitry, such as mixed-signal ASIC designs. This flow supports fast-turnaround environments where ECO requests occur frequently but remain localized, and ECO windows are short.

• 2-stage ECO flow (Green): Designed for streamlined handoffs between traditional front-end and back-end design teams, where the front-end covers RTL design, synthesis, and DFT phases.

• 2-stage ECO flow (Yellow): This second variant of the two-stage flow supports designs that require an RTL handoff to the implementation team during the design process.

• 3-stage ECO flow (Orange): Perfect for very large-scale digital ASICs, such as mobile application processors or network switches. This flow targets a well-defined ECO process involving separate RTL design and DFT teams, as well as back-end implementation. Result verification is performed at the synthesis and DFT stages before committing back-end changes to minimize risk.

• 4-stage ECO flow (Purple): Tailored for ultra-large ASIC designs such as GPUs or AI server chips, this flow excels in environments where the chip comprises many replicated or hierarchical blocks. It includes a floorplanning step to adjust the patch logic before place and route (P&R) using physical guidance — particularly when the distance between blocks impacts patch timing.

Easy-Logic will showcase its new functional ECO environment at DAC 2025, taking place June 22–25 in San Francisco (Booth # 2521). Visitors are encouraged to schedule detailed discussions in advance to explore how EasylogicECO can be seamlessly integrated into their design environments. To get in touch, please use our Contact Us form at https://www.easylogiceda.com/en/contact.html.

About Easy-Logic Technology

Easy-Logic Technology is a leading provider of cutting-edge functional ECO solutions in the semiconductor industry. With a focus on innovation and customer satisfaction, Easy-Logic Technology delivers advanced tools and technologies that enable its customers to achieve excellence in ASIC design.

Media Contact:

Jimmy Chen

Product Marketing Director

Easy-Logic Technology Limited

Phone: (408)718-2978

Email: jimmy@easylogiceda.com

Website: www.easylogiceda.com/en

Link to Press Release