Arthur Hanson

Well-known member

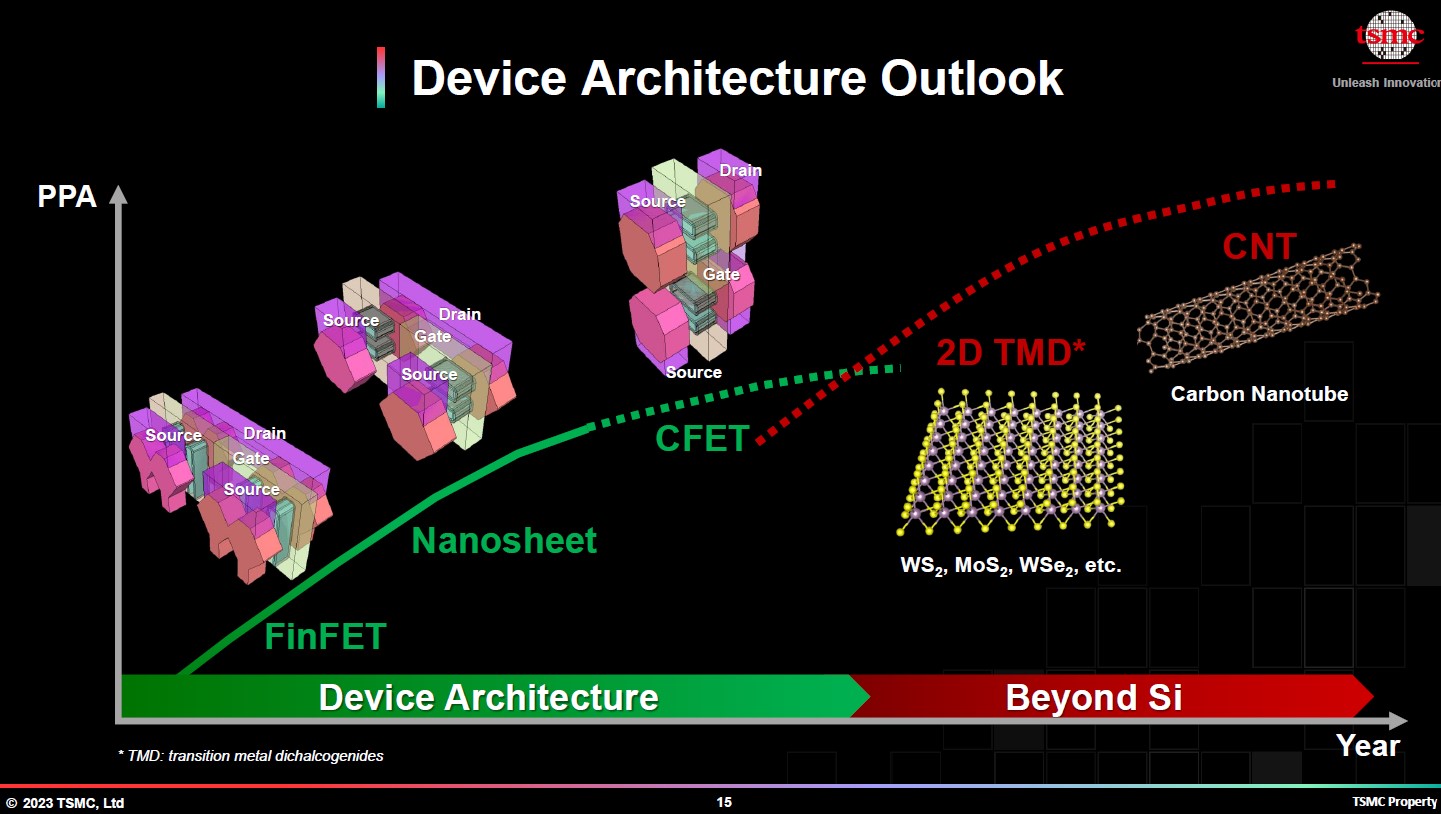

With shrink reaching it physical limits what will be the next areas for advancing computational power and speed? Will TSM still be the leader in five years? Are optical chips on the horizon or will they remain a scientific curiosity? Will cost be the next area of competition as shrink ends? Also, any thoughts on the cost/performance factors of newer technologies would be appreciated.