Collaboration on AI-Driven Design Flows for Optimization and Productivity, Advancements in Photonic IC Integration, Plus Broad IP Development on TSMC 2nm Technology

Highlights:

"Our close collaboration with Open Innovation Platform (OIP)® ecosystem partners like Synopsys has enabled customers to address the most challenging design requirements, all at the leading edge of innovation from angstrom-scale devices to complex multi-die systems across a range of high-performance computing designs," said Dan Kochpatcharin, head of Design Infrastructure Management Division at TSMC. "Together, TSMC and Synopsys will help engineering teams create the next generation of differentiated designs on TSMC's most advanced process nodes with faster time to results."

Certified Digital and Analog Flows on Advanced Nodes

Synopsys' production-ready digital and analog design flows for TSMC N3P and N2 process technologies have been deployed across a range of AI, high-performance computing, and mobile designs. The AI-driven analog design migration flow enables rapid migration from one process node to another. A new flow is available for TSMC N5 to N3E migration, adding to Synopsys' established flows for TSMC N4P to N3E and N3E to N2 processes.

In addition, interoperable process design kits (iPDKs) and Synopsys IC Validator™ physical verification runsets are available for design teams to efficiently transition designs to TSMC advanced process technologies. Synopsys IC Validator enables full-chip physical signoff to handle the increasing complexity of physical verification rules. Synopsys IC Validator is now certified on TSMC N2 and N3P process technologies.

Faster Data Transmission for Multi-Die Designs with Photonic ICs

The high volume of data processing for AI training requires low-latency, power-efficient, and high-bandwidth interconnects, driving the adoption of optical transceivers and near-/co-packaged optics using silicon photonics technology. Synopsys and TSMC are developing end-to-end multi-die electronic and photonic flow solutions for TSMC's Compact Universal Photonic Engine (COUPE) technology to enhance system performance and function. This flow spans photonic IC design with Synopsys OptoCompiler™ and integration with electrical ICs utilizing Synopsys 3DIC Compiler and Ansys multiphysics analysis technologies.

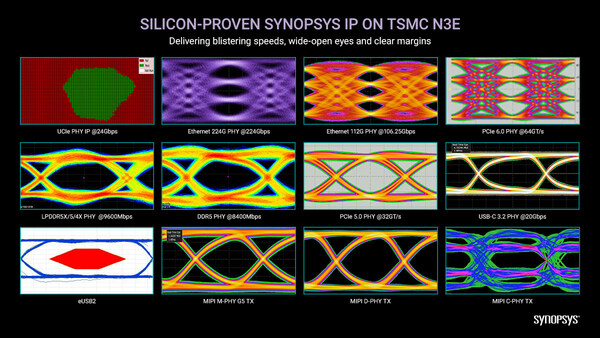

Speed Time-to-Market with Broad IP Portfolio N2 and N2P

Synopsys is developing a broad portfolio of Foundation and Interface IP for the TSMC N2 and N2P process technologies to enable faster silicon success for complex AI, high-performance computing, and mobile SoCs. High-quality PHY IP on N2 and N2P, including UCIe, HBM4/3e, 3DIO, PCIe 7.x/6.x, MIPI C/D-PHY and M-PHY, USB, DDR5 MR-DIMM, and LPDDR6/5x, allows designers to benefit from the PPA improvements of TSMC's most advanced process nodes. In addition, Synopsys provides a silicon-proven Foundation and Interface IP portfolio for TSMC N3P, including 224G Ethernet, UCIe, MIPI C/D-PHY and M-PHY, USB/DisplayPort and eUSB2, LPDDR5x, DDR5, and PCIe 6.x, with DDR5 MR-DIMM in development. Synopsys IP for advanced TSMC processes has been adopted by dozens of leading companies to accelerate their development time.

Availability and Additional Resources

Visit these pages to learn more:

Catalyzing the era of pervasive intelligence, Synopsys, Inc. (Nasdaq: SNPS) delivers trusted and comprehensive silicon to systems design solutions, from electronic design automation to silicon IP and system verification and validation. We partner closely with semiconductor and systems customers across a wide range of industries to maximize their R&D capability and productivity, powering innovation today that ignites the ingenuity of tomorrow. Learn more at www.synopsys.com.

Editorial Contact:

Kelli Wheeler

Synopsys, Inc.

(650) 584-5000

Kelliw@synopsys.com

Corp-pr@synopsys.com

SOURCE Synopsys, Inc.

Link to Press Release

Highlights:

-

SynopsysTSMC-TechSymposium2024

- Production-ready digital and analog design flows, powered by Synopsys.ai™ EDA suite, on TSMC N3/N3P and N2 drive successful results and accelerate analog design migration

- - Certified Synopsys physical verification solution on TSMC N3P and N2 nodes accelerates full-chip physical signoff

- - Collaboration on silicon photonics leveraging Synopsys 3DIC Compiler and Photonics IC solution and TSMC's COUPE technology to further enhance system performance for AI and multi-die designs

- - Broad portfolio of Synopsys Foundation and Interface IP, in development for TSMC N2/N2P, and silicon-proven IP on N3P, shorten design time and reduce integration risk

- SUNNYVALE, Calif., April 24, 2024 /PRNewswire/ -- Synopsys, Inc. (Nasdaq: SNPS) today announced broad EDA and IP collaborations with TSMC for advanced node designs and have been deployed across a range of AI, high-performance computing, and mobile designs. Among the newest collaborations is a co-optimized Photonic IC flow, addressing the application of silicon photonics technology in the quest for better power, performance, and transistor density. Synopsys also noted the industry's confidence in its digital and analog design flows, production-ready for TSMC N3/N3P and N2 process technologies. The two companies are collaborating on next-generation AI-driven flows, including Synopsys DSO.ai™, for design productivity and optimization. In addition, Synopsys is developing a broad portfolio of Foundation and Interface IP on TSMC N2/N2P. In a related announcement today, Keysight, Synopsys, and Ansys introduced a new integrated radio frequency (RF) design migration flow from TSMC's N16 process to its N6RF+ technology.

"Our close collaboration with Open Innovation Platform (OIP)® ecosystem partners like Synopsys has enabled customers to address the most challenging design requirements, all at the leading edge of innovation from angstrom-scale devices to complex multi-die systems across a range of high-performance computing designs," said Dan Kochpatcharin, head of Design Infrastructure Management Division at TSMC. "Together, TSMC and Synopsys will help engineering teams create the next generation of differentiated designs on TSMC's most advanced process nodes with faster time to results."

Certified Digital and Analog Flows on Advanced Nodes

Synopsys' production-ready digital and analog design flows for TSMC N3P and N2 process technologies have been deployed across a range of AI, high-performance computing, and mobile designs. The AI-driven analog design migration flow enables rapid migration from one process node to another. A new flow is available for TSMC N5 to N3E migration, adding to Synopsys' established flows for TSMC N4P to N3E and N3E to N2 processes.

In addition, interoperable process design kits (iPDKs) and Synopsys IC Validator™ physical verification runsets are available for design teams to efficiently transition designs to TSMC advanced process technologies. Synopsys IC Validator enables full-chip physical signoff to handle the increasing complexity of physical verification rules. Synopsys IC Validator is now certified on TSMC N2 and N3P process technologies.

Faster Data Transmission for Multi-Die Designs with Photonic ICs

The high volume of data processing for AI training requires low-latency, power-efficient, and high-bandwidth interconnects, driving the adoption of optical transceivers and near-/co-packaged optics using silicon photonics technology. Synopsys and TSMC are developing end-to-end multi-die electronic and photonic flow solutions for TSMC's Compact Universal Photonic Engine (COUPE) technology to enhance system performance and function. This flow spans photonic IC design with Synopsys OptoCompiler™ and integration with electrical ICs utilizing Synopsys 3DIC Compiler and Ansys multiphysics analysis technologies.

Speed Time-to-Market with Broad IP Portfolio N2 and N2P

Synopsys is developing a broad portfolio of Foundation and Interface IP for the TSMC N2 and N2P process technologies to enable faster silicon success for complex AI, high-performance computing, and mobile SoCs. High-quality PHY IP on N2 and N2P, including UCIe, HBM4/3e, 3DIO, PCIe 7.x/6.x, MIPI C/D-PHY and M-PHY, USB, DDR5 MR-DIMM, and LPDDR6/5x, allows designers to benefit from the PPA improvements of TSMC's most advanced process nodes. In addition, Synopsys provides a silicon-proven Foundation and Interface IP portfolio for TSMC N3P, including 224G Ethernet, UCIe, MIPI C/D-PHY and M-PHY, USB/DisplayPort and eUSB2, LPDDR5x, DDR5, and PCIe 6.x, with DDR5 MR-DIMM in development. Synopsys IP for advanced TSMC processes has been adopted by dozens of leading companies to accelerate their development time.

Availability and Additional Resources

Visit these pages to learn more:

- - Synopsys Digital Design Family: https://www.synopsys.com/implementation-and-signoff/fusion-design-platform.html

- - Synopsys Analog Design Family: https://www.synopsys.com/implementation-and-signoff/custom-design-platform.html

- - Synopsys Multi-Die Solution: https://www.synopsys.com/multi-die-system.html

- - Synopsys Photonic IC Solutions: https://www.synopsys.com/photonic-solutions.html

- - Synopsys IP Portfolio: https://www.synopsys.com/designware-ip.html

Catalyzing the era of pervasive intelligence, Synopsys, Inc. (Nasdaq: SNPS) delivers trusted and comprehensive silicon to systems design solutions, from electronic design automation to silicon IP and system verification and validation. We partner closely with semiconductor and systems customers across a wide range of industries to maximize their R&D capability and productivity, powering innovation today that ignites the ingenuity of tomorrow. Learn more at www.synopsys.com.

Editorial Contact:

Kelli Wheeler

Synopsys, Inc.

(650) 584-5000

Kelliw@synopsys.com

Corp-pr@synopsys.com

SOURCE Synopsys, Inc.

Link to Press Release