You can get there first order quickly (slow down the clocks, etc). Make it functional. You know that they are going to want to jam more stuff in. My point is that there isn't a reason to wait. They can migrating over and prove out what they have without taping out. That is what simulators are for. The US is the safest place to fab a chip right now. In parallel, I assume Intel is willing to provide the first pass conservative rules in 18A with the rev0 models. This also allows the PDK to get flushed out, standard cells, I/O, etc to be created.

Array

(

[content] =>

[params] => Array

(

[0] => /forum/threads/nvidia-once-again-teases-potential-deal-with-intel-says-would-love-to-have-a-third-foundry-partner-besides-tsmc-samsung.19273/page-2

)

[addOns] => Array

(

[DL6/MLTP] => 13

[Hampel/TimeZoneDebug] => 1000070

[SV/ChangePostDate] => 2010200

[SemiWiki/Newsletter] => 1000010

[SemiWiki/WPMenu] => 1000010

[SemiWiki/XPressExtend] => 1000010

[ThemeHouse/XLink] => 1000970

[ThemeHouse/XPress] => 1010570

[XF] => 2021770

[XFI] => 1050270

)

[wordpress] => /var/www/html

)

Guests have limited access.

Join our community today!

Join our community today!

You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please, join our community today!

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

NVIDIA Once Again Teases Potential Deal With Intel: Says Would Love To Have A Third Foundry Partner Besides TSMC & Samsung

- Thread starter Daniel Nenni

- Start date

MKWVentures

Moderator

Lets not make this too complex.

1) Intel is new to foundry. They currently are about 1/30th the size of TSMC in terms of revenue. Intel obviously can make chips and technologies

2) No large company is going to bank on Intel with majority of its volume for several years. They will be tested, then partial volume/backup, then a decision will be made to ramp or not. There will be tons of PR in the mean time.

3) Intel has plans for new technologies, but Intel has a long history of not delivering on time and being very expensive. they need to fix those

4) 18A is the finish line per Pat. According to intel, they need to run multiple Intel internal products before ramping foundry. This is a 2026 foundry ramp at the earliest.

5) Reminder: Intel chooses to run multiple chiplets and entire chips on TSMC.... now and in the future. There might be a reason for that

So aside from details on patterning, DRC, PDK..... Intel has to prove itself before large companies ramp.

Our model shows intel external revenue by year.... it is probably optimistic.... it is less than half of what some people have claimed for Intel Foundry revenue. www.mkwventures.com

1) Intel is new to foundry. They currently are about 1/30th the size of TSMC in terms of revenue. Intel obviously can make chips and technologies

2) No large company is going to bank on Intel with majority of its volume for several years. They will be tested, then partial volume/backup, then a decision will be made to ramp or not. There will be tons of PR in the mean time.

3) Intel has plans for new technologies, but Intel has a long history of not delivering on time and being very expensive. they need to fix those

4) 18A is the finish line per Pat. According to intel, they need to run multiple Intel internal products before ramping foundry. This is a 2026 foundry ramp at the earliest.

5) Reminder: Intel chooses to run multiple chiplets and entire chips on TSMC.... now and in the future. There might be a reason for that

So aside from details on patterning, DRC, PDK..... Intel has to prove itself before large companies ramp.

Our model shows intel external revenue by year.... it is probably optimistic.... it is less than half of what some people have claimed for Intel Foundry revenue. www.mkwventures.com

When Intel tried to be a foundry last time they were not using industry standard EDA, which I heard caused problems when dealing with outside customers. It seems like those days are gone and Intel can certainly take advanced designs to TSMC using tools others use, so they probably have solved that problem. Which is not to say Blue's other concerns are not valid, just that some of them are past.

@Tanj , more like using standard EDA tools in non-standard ways via some proprietary utilities and methodologies grafted on, in a Frankenstein flow kind of approach. Add on that characterization of internal IP, including std. cells, was done for a proprietary (processor) design style, that really couldn't be duplicated by end-users. That Intel designers could use standard design tools in a standard design flow based on standard characterization to fab Intel chips via TSMC, was a total wake-up call for the DT team.

@Tanj , more like using standard EDA tools in non-standard ways via some proprietary utilities and methodologies grafted on, in a Frankenstein flow kind of approach. Add on that characterization of internal IP, including std. cells, was done for a proprietary (processor) design style, that really couldn't be duplicated by end-users. That Intel designers could use standard design tools in a standard design flow based on standard characterization to fab Intel chips via TSMC, was a total wake-up call for the DT team.

Intel is making progress on that front:

Enabling Customers with high-quality IPs from Industry Leaders

https://www.intel.com/content/www/us/en/foundry/accelerator/ip-alliance.html

I think so too ! They have smart people there at IFS who know the foundry business. But the path to TSMC-level enablement is expensive in terms of licensing, test wafers, test vehicle design, and validation. And requires essentially 2-3 years of lead time per node, for the whale customers’ needs.Intel is making progress on that front:

delong.height

Active member

I think it's more of say: customer come to IFS, demanding this and that. IFS looks and see if those can be satisfied. I don't think they have the know-how like TSMC because their knowledge have been accumulating like decades. Even hiring a bunch of people from TSMC/Samsung, you still won't learn all the customer relationship techniques over night. I think the industry knows it and should expect that to happen.The reference I posted said EUV is ready and in production.

Not completely correct. I didn't mention management incompetence. I think it's going to be more of a case of lack of management knowledge and/or experience with best practices in being a foundry. I wonder how many former foundry users are on staff in IFS?

People shouldn't blame them for not having the ability to handle customers' relationship. They are still learning, you just can't expect much from a newcomers.

I don't believe this. Intel has many people in their internal development groups who have been using TSMC and licensed IP for a long time. Intel doesn't have to wait for external customers to make demands or tell them what they need. Intel already has people like that on their payroll.I think it's more of say: customer come to IFS, demanding this and that. IFS looks and see if those can be satisfied. I don't think they have the know-how like TSMC because their knowledge have been accumulating like decades. Even hiring a bunch of people from TSMC/Samsung, you still won't learn all the customer relationship techniques over night. I think the industry knows it and should expect that to happen.

People shouldn't blame them for not having the ability to handle customers' relationship. They are still learning, you just can't expect much from a newcomers.

I think this story about TSMC having some special customer knowledge is probably true for Apple, and it might be true for Nvidia (because I'm told having big die capabilities is different for every process generation), but for customers more interested in chiplet designs, the TSMC customer magic story seems solvable to a foundry that employs a lot of external customers who have dependencies on licensed IP. The only reason I can think of that IFS doesn't have a handle on customer needs is IFS incompetence.

Nvidia is fully committed to TSMC N3 and N2. For Samsung it is legacy products. I seriously doubt Nvidia will split the manufacturing of a single chip between two fabs. That has not worked in the past. But as I said, tossing in a chiplet from IFS should not be a problem and it will be a great press release. Not much revenue however. Nvidia could also use IFS for packaging but again, not great margins.

Nvidia was one of the companies that stepped up and said they wanted to use TSMC AZ but since AZ is a node behind it would be back-up manufacturing versus leading edge but manufacturing just the same.

Nvidia was one of the companies that stepped up and said they wanted to use TSMC AZ but since AZ is a node behind it would be back-up manufacturing versus leading edge but manufacturing just the same.

What do you mean by backup manufacturing?Nvidia is fully committed to TSMC N3 and N2. For Samsung it is legacy products. I seriously doubt Nvidia will split the manufacturing of a single chip between two fabs. That has not worked in the past. But as I said, tossing in a chiplet from IFS should not be a problem and it will be a great press release. Not much revenue however. Nvidia could also use IFS for packaging but again, not great margins.

Nvidia was one of the companies that stepped up and said they wanted to use TSMC AZ but since AZ is a node behind it would be back-up manufacturing versus leading edge but manufacturing just the same.

Do you think TSMC's node-behind model for the AZ fabs can be an economic success?

What do you mean by backup manufacturing?

Do you think TSMC's node-behind model for the AZ fabs can be an economic success?

Manufacturing can be reallocated from Taiwan to AZ for N4/3 products. Yes AZ will be an economic success. TSMC got billions of dollars in CHIPs Act money and AZ Gov money. I'm sure TSMC AZ will do fine. I'm not sure if TSMC will build more fabs in AZ though. I will be at the TSMC conference in two weeks. I will ask.

hist78

Well-known member

I think it's more of say: customer come to IFS, demanding this and that. IFS looks and see if those can be satisfied. I don't think they have the know-how like TSMC because their knowledge have been accumulating like decades. Even hiring a bunch of people from TSMC/Samsung, you still won't learn all the customer relationship techniques over night. I think the industry knows it and should expect that to happen.

People shouldn't blame them for not having the ability to handle customers' relationship. They are still learning, you just can't expect much from a newcomers.

As a very late entrant to the foundry business, Intel should not attempt to provide the same services or compete directly in the same market as incumbents like TSMC or Samsung. If Intel cannot differentiate itself and find a sizable market segment that has not already been addressed by those incumbents, then Intel should not enter the foundry business at all.

As a very late entrant to the foundry business, Intel should not attempt to provide the same services or compete directly in the same market as incumbents like TSMC or Samsung. If Intel cannot differentiate itself and find a sizable market segment that has not already been addressed by those incumbents, then Intel should not enter the foundry business at all.

Exactly! It is all about differentiating. Globalfoundries did a nice pivot to differentiate and have done quite well with limited CAPEX.

Intel try to enter the advanced node market. Unfortunately tsmc cover everything beyond 7nm so Intel directly compete with tsmc everywhere. (That’s also why I think it’s laughable that Rapidus said they will not directly compete with tsmc)As a very late entrant to the foundry business, Intel should not attempt to provide the same services or compete directly in the same market as incumbents like TSMC or Samsung. If Intel cannot differentiate itself and find a sizable market segment that has not already been addressed by those incumbents, then Intel should not enter the foundry business at all.

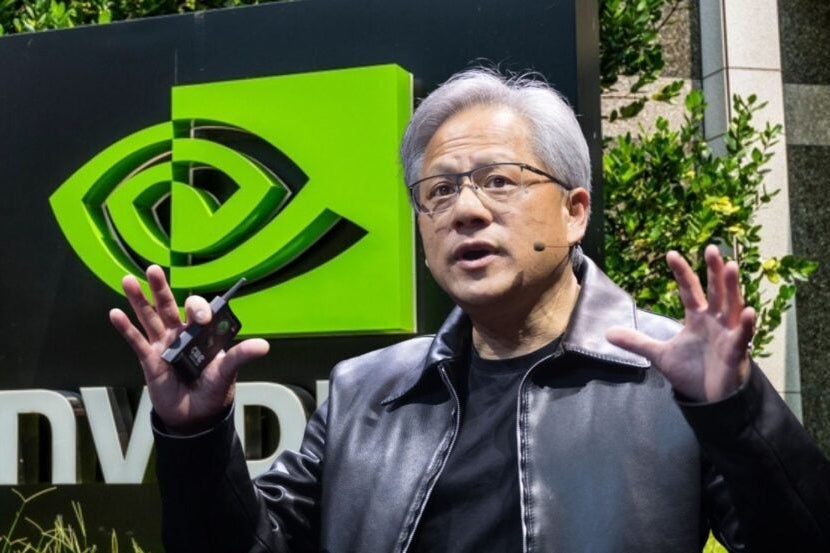

Nvidia CEO Jensen Huang Admits 'It's Tense' As Surging Demand For Blackwell Chips Sparks Customer Frustration - NVIDIA (NASDAQ:NVDA)

Nvidia CEO Jensen Huang said some Nvidia customers are becoming frustrated and tensions are rising due to the limited supply of the company's latest Blackwell chips.

He also addressed concerns related to the rising geopolitical tensions surrounding key Nvidia-supplier, Taiwan Semiconductor Manufacturing Company Ltd. TSM. Huang speculated that Nvidia could switch suppliers if it becomes necessary, but warned that such a change could result in lower-quality products.

The Nvidia CEO said the company chooses to use TSMC because it is the best in the field and its "agility and their capability to respond to our needs is just incredible," he said. "And so we use them because they're great, but if necessary, of course, we can always bring up others."