Looks like 6X GP, 4X MP to me, roughly. So 7-nm class. Style looks TSMC-like.The gate patch CDs are somewhat relaxed compared to other 7nm process nodes, but still shrunk compared to SMICs N+1 version. This suggests the gate density is less versus other 7nm devices in the market. However, with other design-technology co-optimization (DTCO) features implemented on this die, like single diffusion break (SDB).the gate density gap is reduced.

Lower metal layers feature similar routing strategies to SMIC's N+1 version, but with smaller CDs bring this SMIC N+2 process closer to other 7nm nodes. These enhancerments enabled SMIC to shrink its standard cell height (-5%) and standard cell area (-10%) compared to its N+1 implementation.

Discovering a Kirin 9000s chip uting SMIC's 7nm (N+2) foundry process in the new Huawei Mate 60 Pro smartphone demonstrates the technical progress China's semiconductor industry has been able to make without EUV lithography tools.

View attachment 1419

Array

(

[content] =>

[params] => Array

(

[0] => /forum/threads/kirin-9000s-analysis-should-be-made-by-smics-n-2-process.18682/page-2

)

[addOns] => Array

(

[DL6/MLTP] => 13

[Hampel/TimeZoneDebug] => 1000070

[SV/ChangePostDate] => 2010200

[SemiWiki/Newsletter] => 1000010

[SemiWiki/WPMenu] => 1000010

[SemiWiki/XPressExtend] => 1000010

[ThemeHouse/XLink] => 1000970

[ThemeHouse/XPress] => 1010570

[XF] => 2021770

[XFI] => 1050270

)

[wordpress] => /var/www/html

)

Guests have limited access.

Join our community today!

Join our community today!

You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please, join our community today!

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Kirin 9000s Analysis: Should be Made by SMIC's N+2 Process

- Thread starter Maximus

- Start date

But I agree that it is possible that SMIC didn't make the chip,rather they have licensed their N+2 IP to Huawei,Huawei made the chip at their own fab.

The only fab capable of making such chips in China is SMIC's Shanghai Zhangjiang fab. But it has less than 30K per month installed capacity. This capacity will be reduced substantially when and if the process requires multi-patterning (many more dep/pattern/etch steps) because of the lack of advanced lithography, as many in this forum believe they do and there is no way around it.

For Huawei to sell 20m phones annually (as some media estimated or "hyped"), with the reduced capacity due to multi-patterning and most likely lower yield, there is NO way SMIC will be able to produce enough chips to support that kind of volume, even if it dedicates the entire 100% of this fab's capacity to Huawei (which is another impossibility as I am sure China has other more important priorities than making the stupid mobile phones).

It's is entirely possible for Huawei to secretly build its own fabs and capacity, but without the participation of the global equipment giants, especially ASML, it's entirely NOT possible to have a functioning fab producing advanced 7nm chips. As of today, it's still entirely impossible to equip an entire fab with only China-made equipment for 14nm or below nodes.

This entire Huawei "low-key" 7nm show is just trying to 1) make Washington (and other Western capitals) to believe that "hey look at me! Sanction does not work so you should just drop them...!"; 2) make the executives in companies like Qualcomm's, Mediatek's etc. super worried of their market share and thus pumping up their lobbying efforts to relax/cancel the sanctions, which is exactly Huawei's end goal.

I think the folks in Washington are smart enough to not fall for Huawei's trick. More likely, I think they may react to further tighten the sanction rules, as some people in Congress already making such noise.

Huawei's new smartphone uses more China-made parts than previous models-TechInsights

Huawei Technologies' new high-end smartphone contains more China-made chip components than previous models in a sign of Beijing's advances in the semiconductor sphere, according to research firm TechInsights, which is taking the device apart. The Ottawa-based firm has since last weekend been...

Huawei's new smartphone uses more China-made parts than previous models-TechInsights

Huawei Technologies' new high-end smartphone contains more China-made chip components than previous models in a sign of Beijing's advances in the semiconductor sphere, according to research firm TechInsights, which is taking the device apart. The Ottawa-based firm has since last weekend been...www.yahoo.com

This is the important part. Techinsights believe that SMIC 7nm yield is above 50%. Not to mention mate60pro is selling at 1000 dollars,I don't think Huawei need gov subsidy for this phone as some have suggested at this price

Some research firms forecast SMIC's 7 nm process has a yield rate below 50%, versus the industry norm of 90% or more, and the low yield would limit shipments to around 2-4 million chips, not enough for Huawei to regain its former smartphone market dominance.

Hutcheson, however, said "above 50%" was reasonable in his view, saying the chip was made in a far cleaner fashion and was much more competent than an earlier iteration of a 7 nm chip also made by SMIC that TechInsights examined last year. "You can tell by how well it's made," he said

The only fab capable of making such chips in China is SMIC's Shanghai Zhangjiang fab. But it has less than 30K per month installed capacity. This capacity will be reduced substantially when and if the process requires multi-patterning (many more dep/pattern/etch steps) because of the lack of advanced lithography, as many in this forum believe they do and there is no way around it.

For Huawei to sell 20m phones annually (as some media estimated or "hyped"), with the reduced capacity due to multi-patterning and most likely lower yield, there is NO way SMIC will be able to produce enough chips to support that kind of volume, even if it dedicates the entire 100% of this fab's capacity to Huawei (which is another impossibility as I am sure China has other more important priorities than making the stupid mobile phones).

Huawei sold 800k Mate60pro on the very first day,so I don't think 20m annually is farfetched. And if they do actually ship tens of millions of phones annually,that means there is no shortage on 7nm capacity

It's is entirely possible for Huawei to secretly build its own fabs and capacity, but without the participation of the global equipment giants, especially ASML, it's entirely NOT possible to have a functioning fab producing advanced 7nm chips. As of today, it's still entirely impossible to equip an entire fab with only China-made equipment for 14nm or below nodes.

Who said Huawei only uses domestic equipments?That's not what I have heard. Huawei bought lots of second hand equipments,including ASML machines.

This entire Huawei "low-key" 7nm show is just trying to 1) make Washington (and other Western capitals) to believe that "hey look at me! Sanction does not work so you should just drop them...!"; 2) make the executives in companies like Qualcomm's, Mediatek's etc. super worried of their market share and thus pumping up their lobbying efforts to relax/cancel the sanctions, which is exactly Huawei's end goal.

For a phone that is being sold at 1000 dollars and super popular in China,there is big profit to be made,Huawei is doing it for business.

I think the folks in Washington are smart enough to not fall for Huawei's trick. More likely, I think they may react to further tighten the sanction rules, as some people in Congress already making such noise.

Oh yes,Huawei or SMIC is fully anticipating this to happen. Any idiot knows that in light of current political atmosphere in the US,no politician dare to be soft on China,so the only possible reaction from the US is further tighten the sanction rules. The message from huawei to the US is clear,"a slap in the face, what're you going to do about it?"

This is the important part. Techinsights believe that SMIC 7nm yield is above 50%. Not to mention mate60pro is selling at 1000 dollars,I don't think Huawei need gov subsidy for this phone as some have suggested at this price

I know the guy quoted and this is not a credible yield reference. We do not know how long SMIC has been making the chips so they could have stock piled them before the official release.

Huawei sold 800k Mate60pro on the very first day,so I don't think 20m annually is farfetched. And if they do actually ship tens of millions of phones annually,that means there is no shortage on 7nm capacity

Who said Huawei only uses domestic equipments?That's not what I have heard. Huawei bought lots of second hand equipments,including ASML machines.

For a phone that is being sold at 1000 dollars and super popular in China,there is big profit to be made,Huawei is doing it for business.

Oh yes,Huawei or SMIC is fully anticipating this to happen. Any idiot knows that in light of current political atmosphere in the US,no politician dare to be soft on China,so the only possible reaction from the US is further tighten the sanction rules. The message from huawei to the US is clear,"a slap in the face, what're you going to do about it?"

$1000 is expensive for a non-leading edge phone do you not think?

Anyway more power to them.

I assume Samsung will be sweating as this phone is fishing in same pond as them in this price range.

$1000 is expensive for a non-leading edge phone do you not think?

Anyway more power to them.

I assume Samsung will be sweating as this phone is fishing in same pond as them in this price range.

Huawei has always been the premier brand in China,no matter how powerful Qualcomm chip is,other Android brand can never compete with Huawei in high end market in China,or sell phones as pricey as huawei does. That's just the reality in Chinese market

SMIC N+2 in Huawei Mate Pro 60 - Semiwiki

Up until last December I was president and owner of IC Knowledge LLC, at the end of November, I sold IC Knowledge LLC to TechInsights. It has been interesting to become an insider at the world’s leading semiconductor reverse engineering and knowledge company. The latest SMIC N+2 analysis is an...

M. Y. Zuo

Active member

Aren't some of Samsung's folding phones >$2000 USD?Huawei has always been the premier brand in China,no matter how powerful Qualcomm chip is,other Android brand can never compete with Huawei in high end market in China,or sell phones as pricey as huawei does. That's just the reality in Chinese market

hist78

Well-known member

The only fab capable of making such chips in China is SMIC's Shanghai Zhangjiang fab. But it has less than 30K per month installed capacity. This capacity will be reduced substantially when and if the process requires multi-patterning (many more dep/pattern/etch steps) because of the lack of advanced lithography, as many in this forum believe they do and there is no way around it.

For Huawei to sell 20m phones annually (as some media estimated or "hyped"), with the reduced capacity due to multi-patterning and most likely lower yield, there is NO way SMIC will be able to produce enough chips to support that kind of volume, even if it dedicates the entire 100% of this fab's capacity to Huawei (which is another impossibility as I am sure China has other more important priorities than making the stupid mobile phones).

It's is entirely possible for Huawei to secretly build its own fabs and capacity, but without the participation of the global equipment giants, especially ASML, it's entirely NOT possible to have a functioning fab producing advanced 7nm chips. As of today, it's still entirely impossible to equip an entire fab with only China-made equipment for 14nm or below nodes.

This entire Huawei "low-key" 7nm show is just trying to 1) make Washington (and other Western capitals) to believe that "hey look at me! Sanction does not work so you should just drop them...!"; 2) make the executives in companies like Qualcomm's, Mediatek's etc. super worried of their market share and thus pumping up their lobbying efforts to relax/cancel the sanctions, which is exactly Huawei's end goal.

I think the folks in Washington are smart enough to not fall for Huawei's trick. More likely, I think they may react to further tighten the sanction rules, as some people in Congress already making such noise.

"For Huawei to sell 20m phones annually (as some media estimated or "hyped"), with the reduced capacity due to multi-patterning and most likely lower yield, there is NO way SMIC will be able to produce enough chips to support that kind of volume, even if it dedicates the entire 100% of this fab's capacity to Huawei (which is another impossibility as I am sure China has other more important priorities than making the stupid mobile phones)."

If this annual 20 million units of Mate 60 sales forecast is correct, or let's increase it to 40 million units a year, it's already a clear indication that Huawei and SMIC are facing serious yield, cost, component shortages, and/or capacity problems for the Mate 60 and Kirin 9000s chips production.

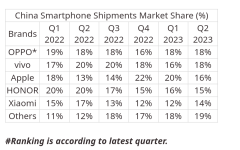

No matter 20 million units or 40 million units a year for the Mate 60, it's only equivalent to a month or a quarter of smartphone sales for each of the top 5 global smartphone manufacturers. This relatively small unit sales number is probably because Kirin 9000s is a very expensive, low yield, and low output capacity product.

Source: https://www.counterpointresearch.com/insights/global-smartphone-share/

Aren't some of Samsung's folding phones >$2000 USD?

Yes,but no one buys Samsung in China

hist78

Well-known member

Aren't some of Samsung's folding phones >$2000 USD?

Despite various challenges, Samsung grew its foldable phone market share in China from 6% in Q1 2022 to 26% in Q1 2023.

Source: https://www.counterpointresearch.co...ne-market-continues-expand-underpinned-china/

Apple has fallen out of favor in China?

Do the new Huawei phones have government sponsored operating systems? Or standard Android?

Do the new Huawei phones have government sponsored operating systems? Or standard Android?

hist78

Well-known member

Apple has fallen out of favor in China?

Do the new Huawei phones have government sponsored operating systems? Or standard Android?

Apple smartphone market share in China has been up and down but consistently stays at third place for a while. See the picture below.

Source: https://www.counterpointresearch.com/insights/china-smartphone-share/

Huawei Mate 60 has its own OS called HarmonyOS 4.0. Huawei claims it's not an Android clone.

Attachments

freshshine1

New member

China’s chip maker Jiangsu Advanced Memory Semiconductor enters bankruptcy and liquidation after failing to secure new rounds of financing

This news was brought up recently (pardon I could not find a more credible source in English) and I am sure there are some more that are not being reported.

AMS was a joint venture established in 2016 aimed to become a 12-inch wafer fab with an initial investment of $1.78 billion USD. They even had a 1950Hi ASML lithography machine.

They filed for bankruptcy in July and is looking to auction off the equipments, product yield was rumored super horrible at 1.7%.

If companies like Huawei are looking for existing equipments there are plenty to go around.

This news was brought up recently (pardon I could not find a more credible source in English) and I am sure there are some more that are not being reported.

AMS was a joint venture established in 2016 aimed to become a 12-inch wafer fab with an initial investment of $1.78 billion USD. They even had a 1950Hi ASML lithography machine.

They filed for bankruptcy in July and is looking to auction off the equipments, product yield was rumored super horrible at 1.7%.

If companies like Huawei are looking for existing equipments there are plenty to go around.

Hunterdolphin

New member

This is absolutely incorrect. Most export licenses in the last four years have been approved for the company Semiconductor Manufacturing International Corp (SMIC). Over nine out of ten export licenses to SMIC were granted that encompassed a total of 188 licenses valued at nearly $42 billion. Even if SMIC licence was not approved, there are ways to get it though a secondary distributor.The article is Taiwanese,not Chinese.

The author claims that SMIC somehow get an "export license" from the US to make 7nm chip for Huawei,this is nonsense. Firstly,SMIC making anything below 28nm is "illegal" by US standard. Secondly,the US would never approve any fab to make 7nm chips for Huawei. Thirdly,why would SMIC need US "export license" in the first place,since they can operate 7nm production line without input from US companies(US companies cannot help SMIC anything on sub 28nm by law)now?

They didn't do electronmicroscope inspection,everything they said is all speculation. No one knows whats really inside the chip until thorough inspection

/cloudfront-us-east-2.images.arcpublishing.com/reuters/JRJKZI73EFOMBHVMFI3LGA2HOU.jpg)

Huawei, SMIC suppliers received billions worth of licenses for U.S. goods

Suppliers to Chinese telecoms giant Huawei and China's top chipmaker SMIC got billions of dollars worth of licenses from November through April to sell them goods and technology despite their being on a U.S. trade blacklist, documents released by Congress showed on Thursday.

China domestic semiconductor equipment industry does not have the capacity to meet the demands for large manufacturing at any node beyond 28 nm. The company of SMIC is still heavily reliant on western semiconductor equipment technology, and its continued operation supplies for its advance nodes. In particular the technology from companies such as Applied Material, Lam Research, KLA Corporation and ASML-Cymer. For example, Applied Materials sold 7.2 billion dollars of products to mainland China in 2022. This is larger than any nation. While mainland China made up the largest market for Lam Research at 25% of there total sales

Last edited:

They utilize their own operating system called "Harmony OS." Harmony OS is a blend of two elements - one catering to the Internet of Things, and the other is a fork of the Android operating system, although they do not officially acknowledge this.Apple has fallen out of favor in China?

Do the new Huawei phones have government sponsored operating systems? Or standard Android?

Gradually, their strategy of imitating until success has started bearing fruit. By gradually replacing existing components with their own code, they can now confidently assert that Harmony OS is distinct from Android. This also grants them the advantage of optimizing their smartphones since they have full control over both the 9000s chip and the operating system.

However, due to the absence of Google Mobile Services (GMS) support, it is uncertain how well these devices will perform outside of the Chinese market.

China’s chip maker Jiangsu Advanced Memory Semiconductor enters bankruptcy and liquidation after failing to secure new rounds of financing

This news was brought up recently (pardon I could not find a more credible source in English) and I am sure there are some more that are not being reported.

AMS was a joint venture established in 2016 aimed to become a 12-inch wafer fab with an initial investment of $1.78 billion USD. They even had a 1950Hi ASML lithography machine.

They filed for bankruptcy in July and is looking to auction off the equipments, product yield was rumored super horrible at 1.7%.

If companies like Huawei are looking for existing equipments there are plenty to go around.

That's a huge hit, and it's remarkable they got no bailout, nor rescue from at least a private profit interest, while from the premise, it looked to be a company backed by a Qinghua university investment arm (and that's a government university, there are no private universities in China.)

I don't know whether them evoking their closeness to the Chinese government was a real deal, or just a deliberate bid to attract money.