6 Jan 2025

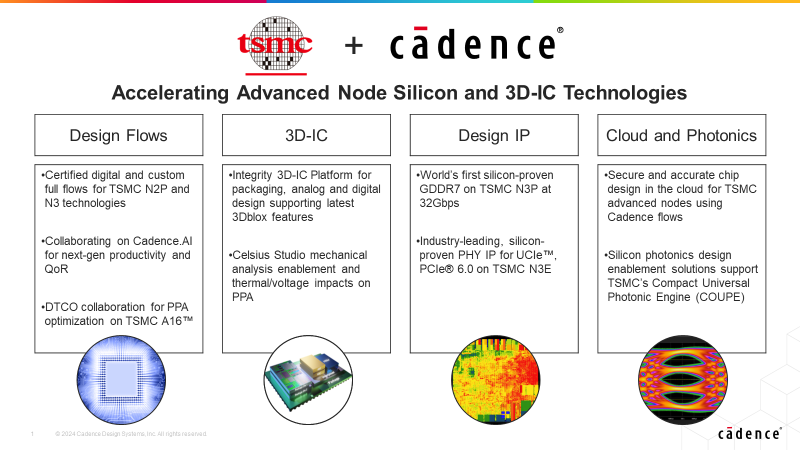

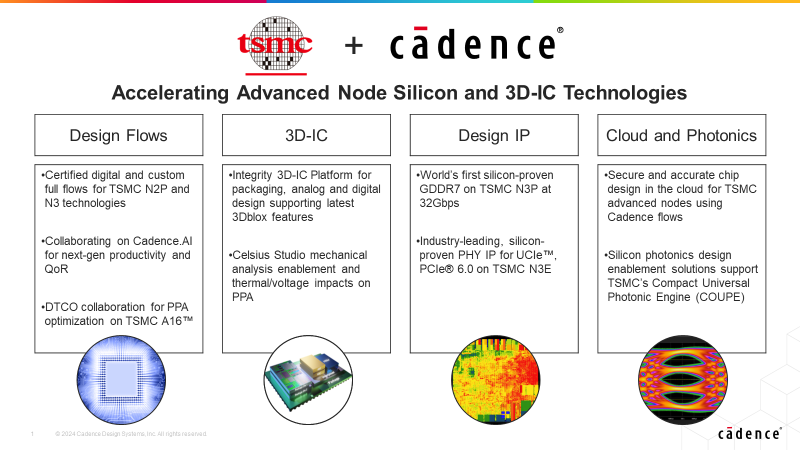

The rapid evolution of artificial intelligence (AI) has positioned it as a driving force in today's semiconductor industry. With the insatiable demand for AI-driven computation and memory-heavy applications, traditional monolithic designs are struggling to keep up. To address this, innovative approaches like chiplets and three-dimensional integrated circuits (3D-IC) are reshaping the design landscape. Cadence and TSMC are at the forefront of this revolution, collaborating to deliver groundbreaking solutions for advanced-node silicon and 3D-IC technologies.

This blog explores how the Cadence's collaboration with TSMC is empowering engineers, innovators, and semiconductor businesses to leverage AI-driven design technology to push the limits of productivity, design performance, and scalability designing 3D-ICs.

Chiplets and 3D-IC are not just a trend; they are becoming the norm, especially in applications like AI inference, where massive amounts of data must flow seamlessly between processing cores and memory.

Read more about Cadence advanced-node design solutions.

Cadence and TSMC are also collaborating on Cadence.AI to drive next-generation digital and analog design automation fueled by AI, delivering industry-leading productivity and quality of results. Cadence.AI is a chips-to-systems AI platform spanning all aspects of design and verification. The collaboration between Cadence and TSMC is focused on three main domains:

Key features include:

Read more about the Cadence Celsius Studio Platform electrothermal solution.

Cadence and TSMC are jointly collaborating with the leaders in the automotive space. As the silicon content in today's automotive designs continues to grow, IP development for current and future process nodes, such as TSMC N5A and later N3A, is even more critical.

Read more about Cadence advanced-node silicon IP solutions.

Read more about Cadence Cloud services.

Read more about Cadence Photonics Design Flows.

Watch the video about the TSMC Collaboration Awards.

Want to learn more about these cutting-edge solutions? Visit our website to explore the latest in Cadence-TSMC technology breakthroughs.

Link to Press Release

The rapid evolution of artificial intelligence (AI) has positioned it as a driving force in today's semiconductor industry. With the insatiable demand for AI-driven computation and memory-heavy applications, traditional monolithic designs are struggling to keep up. To address this, innovative approaches like chiplets and three-dimensional integrated circuits (3D-IC) are reshaping the design landscape. Cadence and TSMC are at the forefront of this revolution, collaborating to deliver groundbreaking solutions for advanced-node silicon and 3D-IC technologies.

This blog explores how the Cadence's collaboration with TSMC is empowering engineers, innovators, and semiconductor businesses to leverage AI-driven design technology to push the limits of productivity, design performance, and scalability designing 3D-ICs.

The AI-Driven Shift in Semiconductor Design

AI technology is rapidly proliferating to multiple applications, necessitating 3D-IC to overcome massive IP integration limitations of single die chips. AI is also transforming the design process itself to overcome the complexity challenges of these large multi-die systems.The Challenges of Compute-Limited Technologies

The rise of AI has placed unprecedented demands on semiconductor performance for compute-heavy workloads. Traditional monolithic system-on-chips (SoCs) face bottlenecks not in raw computational power but in memory and data communication bandwidth. Progress is further constrained by the reticle limit, which restricts the size of heterogeneous designs on a single chip.The Breakthrough of 3D-IC and Chiplets

Enter the chiplets and 3D-IC technologies. These approaches enable designers to partition large designs into smaller, modular components (chiplets) that can be stacked or integrated into compact packaging forms. This paradigm shift allows for better system performance, higher yield, and lower production costs—all without being limited by reticle size.Chiplets and 3D-IC are not just a trend; they are becoming the norm, especially in applications like AI inference, where massive amounts of data must flow seamlessly between processing cores and memory.

The Role of Collaboration

To meet these changing demands head-on, Cadence has partnered with TSMC to supply industry-leading design infrastructure, advanced 3D-IC platforms, silicon-proven IP, and AI-driven design tools available in the cloud. This partnership underscores their shared mission to fuel AI innovation through breakthrough semiconductor technologies.

Certified Design Flows and AI-Driven Design

TSMC technology provides design opportunities and requires specific design methodology to ensure tapeout success and high-yield growth.Advanced-Node Design Flows

TSMC has certified Cadence's industry-leading digital and custom design flows for implementation and signoff on TSMC's latest N3 and N2P process technologies. As long-standing design technology co-optimization (DTCO) partners, TSMC and Cadence continue that tradition by collaborating to optimize power, performance, and area (PPA) on TSMC A16™, adding EDA features to enable advanced features such as backside routing.Read more about Cadence advanced-node design solutions.

Cadence and TSMC are also collaborating on Cadence.AI to drive next-generation digital and analog design automation fueled by AI, delivering industry-leading productivity and quality of results. Cadence.AI is a chips-to-systems AI platform spanning all aspects of design and verification. The collaboration between Cadence and TSMC is focused on three main domains:

- The Cadence Cerebrus Intelligent Chip Explorer applies AI to digital design for converging on the optimal PPA.

- The Cadence Joint Enterprise Data and AI (JedAI) Platform uses generative AI for design debug and analytics, helping with PPA analysis.

- Cadence's Virtuoso Studio enables migrating legacy custom and analog designs to modern nodes and performs circuit optimization and high-sigma Monte Carlo analysis.

3D-IC Platform Innovations

TSMC is leading the industry in 3D-IC technology, enabling new design architectures and requiring new design technology.Integrity 3D-IC Platform

The Cadence Integrity 3D-IC Platform is a leading system-level exploration solution and a single-vendor platform that unifies packaging, analog, and digital implementation—making efficient 3D-IC design possible. This opens new opportunities for innovation by supporting all the latest 3Dblox features and constructs. To enable the ultra-high-density interconnect in TSMC 3DFabric® technologies, TSMC and Cadence are collaborating on a next-generation high-capacity substrate router for die-to-die and die-to-substrate connections.Key features include:

- - Thermal and Warpage Analysis – Perform what-if thermal and mechanical simulations, crucial for stacked chiplets.

- - Chip and Package Co-Design – A constraint-exchange mechanism ensures alignment between IC designers and packaging teams.

- - Multiphysics Analysis – Unified data models enable rapid optimization, balancing thermal, electrical, and voltage impacts.

- - AI-Powered PDN Optimization – Use AI to design power delivery networks (PDNs) with the optimal placement of through silicon vias (TSVs) and bumps for stacked chips.

Celsius Studio for Thermal and Voltage Analysis

Multiphysics analyses and optimization is a critical dimension of success for 3D-IC technologies. Cadence is collaborating with TSMC to enable warpage analysis for TSMC 3DFabric in addition to electrical/thermal analysis, and Cadence's Celsius Studio mechanical warpage analysis simulation results have been validated. Thermal and voltage impacts on power/IR/STA are also enabled and verified inside the Cadence Integrity 3D-IC Platform for TSMC 3DFabric.Read more about the Cadence Celsius Studio Platform electrothermal solution.

Leading Design IP Development

The AI factories' insatiable appetite for data is increasing the requirements for interconnects and pushing power envelopes. Cadence has a broad portfolio of critical IP for efficiently moving data between chiplets and across data centers, including Universal Chiplet Interconnect Express™ (UCIe™) 1.0, PCI Express® (PCIe®) 6.0, and the world's first silicon-proven GDDR7 on TSMC N3, running at 32Gbps, which provides the best price/performance for AI interfaces in both data centers and network edges.Cadence and TSMC are jointly collaborating with the leaders in the automotive space. As the silicon content in today's automotive designs continues to grow, IP development for current and future process nodes, such as TSMC N5A and later N3A, is even more critical.

Read more about Cadence advanced-node silicon IP solutions.

Cloud and Photonics Pioneer

Cloud-based design is enabling faster deployment of process and design technologies.Secure Cloud-Based Design

Cadence solutions support secure and accurate chip design in the cloud, with design solutions to support TSMC leading-edge technologies, allowing teams to reduce their time to market by leveraging the scalability of cloud.Read more about Cadence Cloud services.

Silicon Photonics

Cadence's silicon photonics design solutions, in synergy with TSMC's Compact Universal Photonic Engine (COUPE), enable cutting-edge integration of photonic components for ultra-fast data transmission. This promises significant advancements in networking and high-performance computing.Read more about Cadence Photonics Design Flows.

TSMC OIP® Collaboration Awards 2024

We're honored to be recognized by TSMC for our innovations for:- - TSMC A16 and N2P design infrastructure

- - Multiphysics solutions that break new ground

- - COUPE design solutions that boost productivity

- - RF design migration solutions for seamless transitions

- - Advanced DSP IP enhancing compute performance

Watch the video about the TSMC Collaboration Awards.

Explore the Future of Semiconductor Innovation

Cadence works with TSMC to drive a paradigm shift in semiconductor design, fueled by the powerful combination of AI, 3D-IC technologies, and silicon-proven IP. Their collaboration is making it easier, faster, and more efficient for engineers and innovators to deliver groundbreaking designs.Want to learn more about these cutting-edge solutions? Visit our website to explore the latest in Cadence-TSMC technology breakthroughs.

Link to Press Release