First Dedicated ASIC company to accept 5nm projects

MILPITAS, Calif., Aug. 13, 2020 /PRNewswire/ -- Alchip Technologies to became the first dedicated ASIC company to announce 5nm commercial design readiness and that is accepting 5nm design. First test-chip tape-outs are expected in December.

Alchip's complete 5nm design-to-delivery methodology focuses on minimizing design turnaround time. Physical design attributes include a chiplet technology platform, high performance computing IP portfolio, IP sub-system integration services and the latest 2.5D heterogeneous packaging capabilities.

The company expects that 5nm demand will come initially from high-performance cloud computing applications. Still, Alchip expects that 5nm devices will be 52% smaller, 3% faster, yet use only 36% of the power, compared to current 7nm devices.

Alchip 5nm deigns will draw upon a high-performance computing IP portfolio that includes "best in class" DDR5, GDDR6, HBM2E, HBM3, D2D, PCIe5, 112G serdes IP from Tier 1 providers. Alchip in-house IP sub-system integration services cover PCIe5, DDR5, HBM2E/3, and 112G PAM4 serdes.

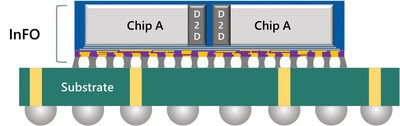

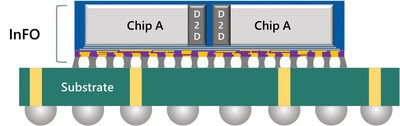

Critical to 5nm production is an innovative advanced packaging capability that is for MCM, CoWoS and InF s. Package design covers SIPI/thermal simulation that provides plug-and-play post silicon solutions to reduce substrate layers and the resulting cost. The result is very elegant 5nm devices with more accurate power and thermal estimation flows for high power designs that have avoided post-silicon surprises.

s. Package design covers SIPI/thermal simulation that provides plug-and-play post silicon solutions to reduce substrate layers and the resulting cost. The result is very elegant 5nm devices with more accurate power and thermal estimation flows for high power designs that have avoided post-silicon surprises.

"We're rolling out our 5nm capabilities now to meet hyper-scalers' demand that is being driven by the work-from-home, online-everything and business continuity surge trends that are driving significant data traffic and demand-pull for compute workloads," said Johnny Shen, Alchip President and CEO. "We've made a commitment to the market that we would meet the demands of advanced technology head-on and today's 5nm announcement substantiates that commitment."

For more information, go to www.alchip.com.

About Alchip

Alchip Technologies Ltd., headquartered in Taipei, Taiwan, is a leading global provider of silicon design and production services for system companies developing complex and high-volume ASICs and SoCs. The company was founded by semiconductor veterans from Silicon Valley and Japan in 2003 and provides faster time-to-market and cost-effective solutions for SoC design at mainstream and advanced, including 7nm processes. Customers include global leaders in AI, HPC/supercomputer, mobile phones, entertainment device, networking equipment and other electronic product categories. Alchip is listed on the Taiwan Stock Exchange (TWSE: 3661) and is a TSMC-certified Value Chain Aggregator.

Alchip's 5nm capabilities will have packaging options that include CoWoS and Info_os (seen here) as part of its feature set.

CONTACT: Chuck Byers, chuck_byers@alchip.com, +1-408-310-9244

This information is being distributed to you by: Alchip Technologies Ltd

1900 McCarthy blvd, suite 106, Milpitas, CA, 95035,

MILPITAS, Calif., Aug. 13, 2020 /PRNewswire/ -- Alchip Technologies to became the first dedicated ASIC company to announce 5nm commercial design readiness and that is accepting 5nm design. First test-chip tape-outs are expected in December.

Alchip's complete 5nm design-to-delivery methodology focuses on minimizing design turnaround time. Physical design attributes include a chiplet technology platform, high performance computing IP portfolio, IP sub-system integration services and the latest 2.5D heterogeneous packaging capabilities.

The company expects that 5nm demand will come initially from high-performance cloud computing applications. Still, Alchip expects that 5nm devices will be 52% smaller, 3% faster, yet use only 36% of the power, compared to current 7nm devices.

Alchip 5nm deigns will draw upon a high-performance computing IP portfolio that includes "best in class" DDR5, GDDR6, HBM2E, HBM3, D2D, PCIe5, 112G serdes IP from Tier 1 providers. Alchip in-house IP sub-system integration services cover PCIe5, DDR5, HBM2E/3, and 112G PAM4 serdes.

Critical to 5nm production is an innovative advanced packaging capability that is for MCM, CoWoS and InF

"We're rolling out our 5nm capabilities now to meet hyper-scalers' demand that is being driven by the work-from-home, online-everything and business continuity surge trends that are driving significant data traffic and demand-pull for compute workloads," said Johnny Shen, Alchip President and CEO. "We've made a commitment to the market that we would meet the demands of advanced technology head-on and today's 5nm announcement substantiates that commitment."

For more information, go to www.alchip.com.

About Alchip

Alchip Technologies Ltd., headquartered in Taipei, Taiwan, is a leading global provider of silicon design and production services for system companies developing complex and high-volume ASICs and SoCs. The company was founded by semiconductor veterans from Silicon Valley and Japan in 2003 and provides faster time-to-market and cost-effective solutions for SoC design at mainstream and advanced, including 7nm processes. Customers include global leaders in AI, HPC/supercomputer, mobile phones, entertainment device, networking equipment and other electronic product categories. Alchip is listed on the Taiwan Stock Exchange (TWSE: 3661) and is a TSMC-certified Value Chain Aggregator.

Alchip's 5nm capabilities will have packaging options that include CoWoS and Info_os (seen here) as part of its feature set.

CONTACT: Chuck Byers, chuck_byers@alchip.com, +1-408-310-9244

This information is being distributed to you by: Alchip Technologies Ltd

1900 McCarthy blvd, suite 106, Milpitas, CA, 95035,