Cambridge, UK 11, July, 2022. Agile Analog™, the analog IP innovators, has announced the availability of its new RC Oscillator IP. This is the first in a new family of analog IP blocks that the company is launching that are designed to make the integration of analog circuits onto ASICs very easy.

“These form part of the library of analog IP circuits that our automatic solution generator, Composa™, uses to create IP blocks that exactly match the requirements of customers,” explained Barry Paterson, Agile Analog’s CEO. “Their modular design means that they can be combined together to form sub-system solutions speeding up design times and reducing risk as they have all been thoroughly tested and verified.”

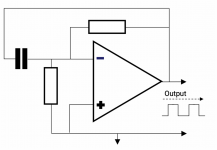

The agileOSC RC is based on a traditional architecture which allows the frequency to be trimmed to remove the effects of process variation. It can also be configured as a Free Running Clock (FRC) where a high accuracy clock is not required. With a start-up time of typically 10 us, it has a frequency range of 20 KHz to 100 MHz with an accuracy of up to +5%. It has a low power consumption of typically 100 uA at 10 MHz which is much less than an equivalent discrete analog component and highlights the benefit of integrating analog circuits onto the main chip.

Composa™

Traditionally, analog IP blocks have to be manually redesigned for each application and process technology but Agile Analog has a unique way to automatically generate analog IP to exactly meet the customer’s specifications and process technology. Called Composa™, it uses tried and tested analog IP circuits that are in the company’s Composa library. Effectively, the design-once-and-re-use-many-times model of digital IP now applies to analog IP for the first time. As the analog IP circuits in the Composa library have been extensively tested and used in previous designs, and are fully validated every time they are generated, this gives a similar level of reassurance to the digital IP world’s ‘silicon-proven’. All the major foundries are supported including TSMC, GlobalFoundries, Samsung Foundry and SMIC as well as other IC foundries and manufacturers.

About Agile Analog Ltd.

Analog IP needs to be different for each design. That is why Agile Analog™ has made a new way of doing things, conceived by some of the best minds in the industry. We provide a wide range of analog IP that is customised to your needs quickly, to a higher quality, and on any semiconductor process. Contact us at www.agileanalog.com to find out more.

Press contact:

Nigel Robson, Vortex PR. nigel@vortexpr.com +44 1481 233080

Agile Analog™ and Composa™ are trademarks of Agile Analog Ltd.

“These form part of the library of analog IP circuits that our automatic solution generator, Composa™, uses to create IP blocks that exactly match the requirements of customers,” explained Barry Paterson, Agile Analog’s CEO. “Their modular design means that they can be combined together to form sub-system solutions speeding up design times and reducing risk as they have all been thoroughly tested and verified.”

The agileOSC RC is based on a traditional architecture which allows the frequency to be trimmed to remove the effects of process variation. It can also be configured as a Free Running Clock (FRC) where a high accuracy clock is not required. With a start-up time of typically 10 us, it has a frequency range of 20 KHz to 100 MHz with an accuracy of up to +5%. It has a low power consumption of typically 100 uA at 10 MHz which is much less than an equivalent discrete analog component and highlights the benefit of integrating analog circuits onto the main chip.

Composa™

Traditionally, analog IP blocks have to be manually redesigned for each application and process technology but Agile Analog has a unique way to automatically generate analog IP to exactly meet the customer’s specifications and process technology. Called Composa™, it uses tried and tested analog IP circuits that are in the company’s Composa library. Effectively, the design-once-and-re-use-many-times model of digital IP now applies to analog IP for the first time. As the analog IP circuits in the Composa library have been extensively tested and used in previous designs, and are fully validated every time they are generated, this gives a similar level of reassurance to the digital IP world’s ‘silicon-proven’. All the major foundries are supported including TSMC, GlobalFoundries, Samsung Foundry and SMIC as well as other IC foundries and manufacturers.

About Agile Analog Ltd.

Analog IP needs to be different for each design. That is why Agile Analog™ has made a new way of doing things, conceived by some of the best minds in the industry. We provide a wide range of analog IP that is customised to your needs quickly, to a higher quality, and on any semiconductor process. Contact us at www.agileanalog.com to find out more.

Press contact:

Nigel Robson, Vortex PR. nigel@vortexpr.com +44 1481 233080

Agile Analog™ and Composa™ are trademarks of Agile Analog Ltd.