Cambridge, UK 11, July, 2022. Agile Analog™, the analog IP innovators, has designed an IR Drop Sensor for its growing library of analog IP. This is an important safety feature for designers as it monitors for voltage drops when current flows through a resistor, which is called IR drop and can affect the timing of a chip and could result in functional failures if this happens in a critical part of the design.

“Adding to the complexity of IR drops, they can be influenced by activity on other areas of the chip so including our agileIR DROP into a design provides real time monitoring of any IR drops caused by power supply fluctuations, hot spots, shorts, etc,” explained Barry Paterson, Agile Analog’s CEO. “It is important to know that IR drops can become worse over the lifetime of a chip hence the need for continual in-chip monitoring. This is caused by electromigration, i.e., over time metal molecules can migrate within wires when currents flow, narrowing them in places which increases the resistance in those locations and results in IR drops.”

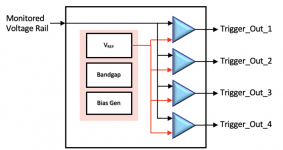

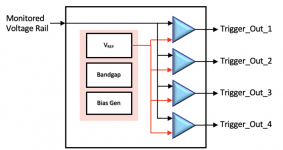

The agileIR Drop consists of a voltage reference and comparator(s) set at different threshold levels for multi-level detection. The number of trigger outputs can be customised, and each threshold can be adjusted during operation to support DVFS operation. A four-output configuration is shown in the block diagram.

It has been designed for low power consumption so that it can be used in battery operated devices if required which will have power supply changes as the cells discharge. The active current is in the order of 120 uA with a power down current of less than 1 uA. As befits a safety device, it has a fast detection time of typically 25 nanoseconds. The threshold accuracy is 5% and 1% when trimmed with a step size of typically 20 mV.

Composa™

Traditionally, analog IP blocks have to be manually redesigned for each application and process technology but Agile Analog has a unique way to automatically generate analog IP to exactly meet the customer’s specifications and process technology. Called Composa™, it uses tried and tested analog IP circuits that are in the company’s Composa library. Effectively, the design-once-and-re-use-many-times model of digital IP now applies to analog IP for the first time. As the analog IP circuits in the Composa library have been extensively tested and used in previous designs, and are fully validated every time they are generated, this gives a similar level of reassurance to the digital IP world’s ‘silicon-proven’. All the major foundries are supported including TSMC, GlobalFoundries, Samsung Foundry and SMIC as well as other IC foundries and manufacturers.

About Agile Analog Ltd.

Analog IP needs to be different for each design. That is why Agile Analog™ has made a new way of doing things, conceived by some of the best minds in the industry. We provide a wide range of analog IP that is customised to your needs quickly, to a higher quality, and on any semiconductor process. Contact us at www.agileanalog.com to find out more.

Press contact:

Nigel Robson, Vortex PR.

nigel@vortexpr.com

+44 1481 233080

Agile Analog™ and Composa™ are trademarks of Agile Analog Ltd.

“Adding to the complexity of IR drops, they can be influenced by activity on other areas of the chip so including our agileIR DROP into a design provides real time monitoring of any IR drops caused by power supply fluctuations, hot spots, shorts, etc,” explained Barry Paterson, Agile Analog’s CEO. “It is important to know that IR drops can become worse over the lifetime of a chip hence the need for continual in-chip monitoring. This is caused by electromigration, i.e., over time metal molecules can migrate within wires when currents flow, narrowing them in places which increases the resistance in those locations and results in IR drops.”

The agileIR Drop consists of a voltage reference and comparator(s) set at different threshold levels for multi-level detection. The number of trigger outputs can be customised, and each threshold can be adjusted during operation to support DVFS operation. A four-output configuration is shown in the block diagram.

It has been designed for low power consumption so that it can be used in battery operated devices if required which will have power supply changes as the cells discharge. The active current is in the order of 120 uA with a power down current of less than 1 uA. As befits a safety device, it has a fast detection time of typically 25 nanoseconds. The threshold accuracy is 5% and 1% when trimmed with a step size of typically 20 mV.

Composa™

Traditionally, analog IP blocks have to be manually redesigned for each application and process technology but Agile Analog has a unique way to automatically generate analog IP to exactly meet the customer’s specifications and process technology. Called Composa™, it uses tried and tested analog IP circuits that are in the company’s Composa library. Effectively, the design-once-and-re-use-many-times model of digital IP now applies to analog IP for the first time. As the analog IP circuits in the Composa library have been extensively tested and used in previous designs, and are fully validated every time they are generated, this gives a similar level of reassurance to the digital IP world’s ‘silicon-proven’. All the major foundries are supported including TSMC, GlobalFoundries, Samsung Foundry and SMIC as well as other IC foundries and manufacturers.

About Agile Analog Ltd.

Analog IP needs to be different for each design. That is why Agile Analog™ has made a new way of doing things, conceived by some of the best minds in the industry. We provide a wide range of analog IP that is customised to your needs quickly, to a higher quality, and on any semiconductor process. Contact us at www.agileanalog.com to find out more.

Press contact:

Nigel Robson, Vortex PR.

nigel@vortexpr.com

+44 1481 233080

Agile Analog™ and Composa™ are trademarks of Agile Analog Ltd.