IDEM and the VLSI symposium have given us a good amount of data to pour over for the node landscape from TSMC and intel in 2023/early 2024. Samsung having declined to give any details on the "in production" 3GAE that has "perfect yields" (their words not mine). I thought it might be nice if that data was complied into one place where everybody could see it.

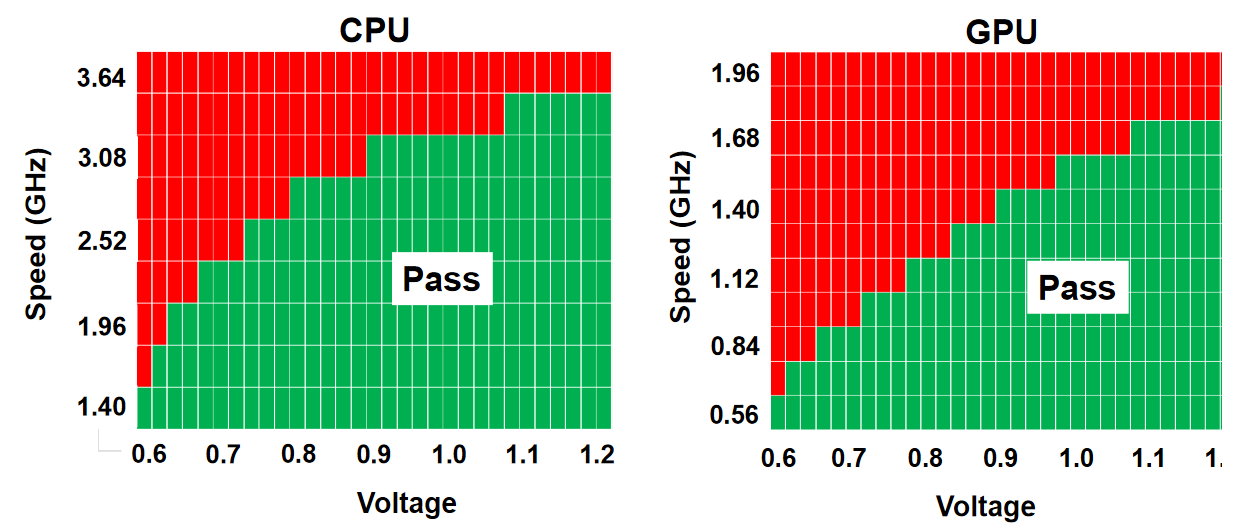

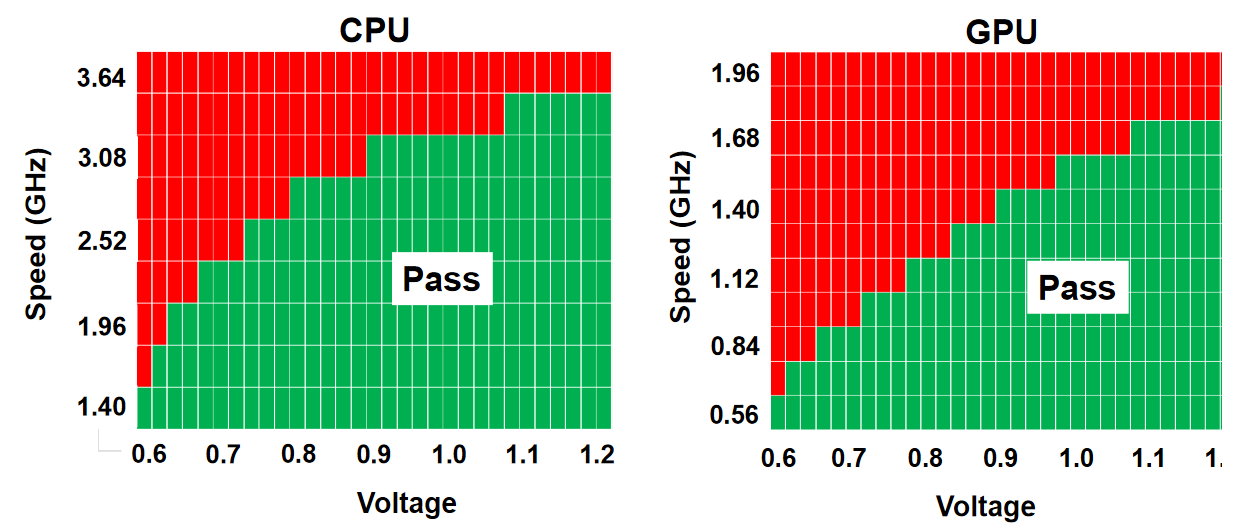

N3B ARM A7 frequency vs voltage passes/fails for 32 different dies:

(no confirmation of fin count was given but presumably this is the 2 fin device)

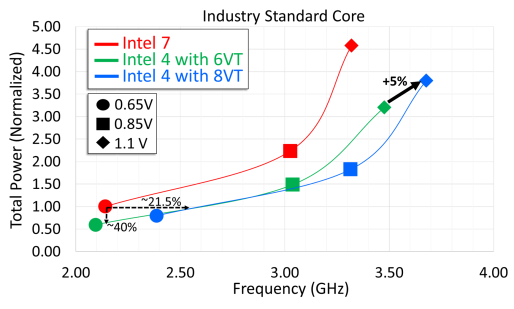

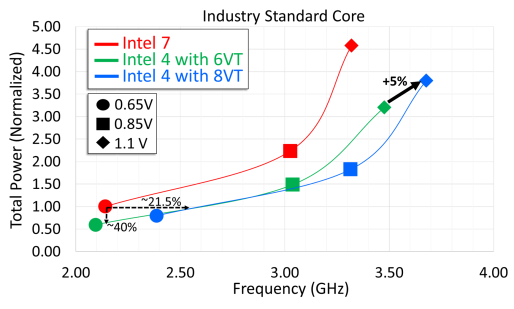

i4 vs i7 normalized power vs frequency curves at varying voltages:

(Since intel has only talked about a 3 fin device, it is assumed that this data is for a 3 fin device vs the 4 fin intel 7 UHP device at 60nm pp)

Voltage (V) ------------------------ GHz on N3B------------------------ GHz on i4 with 6VT

0.65 --------------------------------- 2.0 ----------------------------------- 2.1

0.85 --------------------------------- 2.8 ---------------------------------- ~3.0

1.10 --------------------------------- 3.4 ---------------------------------- ~3.5

(edit sorry for the janky table. I just noticed that the insert table option was only displaying the table as plain text, so I had to manually type up a table)

Across the voltage ranges tested i4 had between a 3% and 7% frequency advantage. This is about in line with Scotten Jones's expectations, and it is highly likely that N3E will catch up to or surpass i4's 6VT version. However it seems like the 8VT version might still be a bit stronger. One observation is that it seems like there is still a good bit of gas in the tank for both flavors of i4 to scale frequency before running up against the same heat output that i7 hits around 3.1 to 3.3 GHz. Additionally TSMC didn't specify which logic libs were being used for this test. So I will assume they were using the mainstream 2-2 fin config. If so then it is probable that the N3 3 fin cells could best intel 4.

Unfortunately we don't have power consumption numbers to compare for these nodes. But from this data performance is definitely competitive. This also means we get to check how AMD and Intel's CPU design teams have been motoring along. The last time we had this opportunity was tigerlake vs Renoir/Cezane, and to a lesser extent Alderlake vs Cezane. With N3E and i4 being so close, Meteorlake and Strix Point will be decided by who has the better architecture and who has the better STCO. Exciting times!

One final tidbit of information is that after having done some digging around it seems like N3B is the first TSMC node to have self aligned contacts. This is odd when one considers that intel has had them since 22nm. It does add some process complexity, but I can't imagine that the extra cost outweighs the extra error margin you get. But who am I tell tell TSMC engineers how to do their jobs. It kind of reminds me of when I learned that the 10LPP family had SDB only to ditch it for 7LPP and bring it back for 5LPE. Of course at the end of the day this doesn't effect how customers will use the end product, but I did find it kind of funky.

As N3E/P/X, 3GAE/GAP, and intel 3 get comparable information revealed I can update these tables.

N3B ARM A7 frequency vs voltage passes/fails for 32 different dies:

(no confirmation of fin count was given but presumably this is the 2 fin device)

i4 vs i7 normalized power vs frequency curves at varying voltages:

(Since intel has only talked about a 3 fin device, it is assumed that this data is for a 3 fin device vs the 4 fin intel 7 UHP device at 60nm pp)

Voltage (V) ------------------------ GHz on N3B------------------------ GHz on i4 with 6VT

0.65 --------------------------------- 2.0 ----------------------------------- 2.1

0.85 --------------------------------- 2.8 ---------------------------------- ~3.0

1.10 --------------------------------- 3.4 ---------------------------------- ~3.5

(edit sorry for the janky table. I just noticed that the insert table option was only displaying the table as plain text, so I had to manually type up a table)

Across the voltage ranges tested i4 had between a 3% and 7% frequency advantage. This is about in line with Scotten Jones's expectations, and it is highly likely that N3E will catch up to or surpass i4's 6VT version. However it seems like the 8VT version might still be a bit stronger. One observation is that it seems like there is still a good bit of gas in the tank for both flavors of i4 to scale frequency before running up against the same heat output that i7 hits around 3.1 to 3.3 GHz. Additionally TSMC didn't specify which logic libs were being used for this test. So I will assume they were using the mainstream 2-2 fin config. If so then it is probable that the N3 3 fin cells could best intel 4.

Unfortunately we don't have power consumption numbers to compare for these nodes. But from this data performance is definitely competitive. This also means we get to check how AMD and Intel's CPU design teams have been motoring along. The last time we had this opportunity was tigerlake vs Renoir/Cezane, and to a lesser extent Alderlake vs Cezane. With N3E and i4 being so close, Meteorlake and Strix Point will be decided by who has the better architecture and who has the better STCO. Exciting times!

One final tidbit of information is that after having done some digging around it seems like N3B is the first TSMC node to have self aligned contacts. This is odd when one considers that intel has had them since 22nm. It does add some process complexity, but I can't imagine that the extra cost outweighs the extra error margin you get. But who am I tell tell TSMC engineers how to do their jobs. It kind of reminds me of when I learned that the 10LPP family had SDB only to ditch it for 7LPP and bring it back for 5LPE. Of course at the end of the day this doesn't effect how customers will use the end product, but I did find it kind of funky.

As N3E/P/X, 3GAE/GAP, and intel 3 get comparable information revealed I can update these tables.

Last edited: