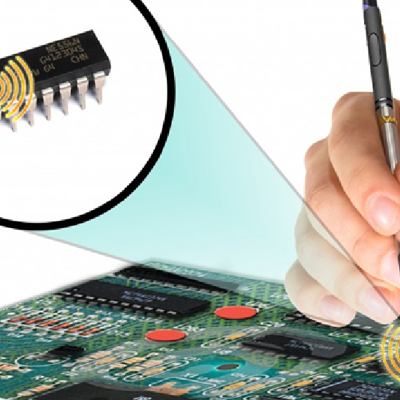

In countries without fabs: Many fabless companies and policy makers to support these fabless companies are wary of sending their tape outs to fabs in foreign countries.

There's a scare that these chips would come with trojans and back doors. And this Huawei tussle is not helping this argument either.

Any EDA tools out there that can do some kind of a check between the silicon and the GDSII to prove that nothing else was added to the chip at the fab end?

If there isn't one there's a big and growing demand for one.

There's a scare that these chips would come with trojans and back doors. And this Huawei tussle is not helping this argument either.

Any EDA tools out there that can do some kind of a check between the silicon and the GDSII to prove that nothing else was added to the chip at the fab end?

If there isn't one there's a big and growing demand for one.

Last edited: