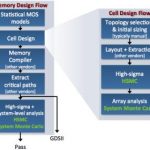

Solido Design Automation and TSMC recently published an article in EE Times describing how Solido’s High-Sigma Monte Carlo tool is used with TSMC PDK’s to achieve high-yield, high-performance memory design. This project has been a big part of my life for the past three years and it is time for a victory lap!

In TSMC 28nm, 20nm and … Read More