Array

(

[content] =>

[params] => Array

(

[0] => /forum/whats-new/latest-activity?before_id=103139

)

[addOns] => Array

(

[DL6/MLTP] => 13

[Hampel/TimeZoneDebug] => 1000070

[SV/ChangePostDate] => 2010200

[SemiWiki/Newsletter] => 1000010

[SemiWiki/WPMenu] => 1000010

[SemiWiki/XPressExtend] => 1000010

[ThemeHouse/XLink] => 1000970

[ThemeHouse/XPress] => 1010570

[XF] => 2030970

[XFI] => 1060170

)

[wordpress] => /var/www/html

)

You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today !

JavaScript is disabled. For a better experience, please enable JavaScript in your browser before proceeding.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an

alternative browser .

K

Appreciate all the discussion and accurate numbers on minimum pitches and raw maximum cell densities, but without any discussion of...

Dec 12, 2025

S

from what I see, there is a increasing interest in startups with 3 letter agencies as their customers. Like any industry, it needs as...

Dec 12, 2025

F

This article explained that some discrepancies may arise, depending on the layout assumptions, such as the ratio of NAND to Flip-Flop...

Dec 12, 2025

A

there have been increased energy in photonics over the years. data communication is what's getting most attention. OCS by google proves...

Dec 12, 2025

V

TechInsights has completed an exploratory teardown and process analysis of the Huawei Kirin 9030 application processor used in the new...

Dec 12, 2025

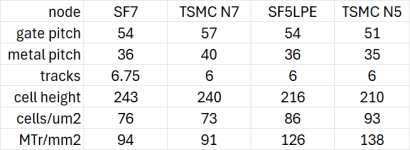

Just a spot check, the Semiwiki article on TSMC N5, has:

171 MTr/mm2, but agrees with 51 and 57 gate pitches for N5 and N7...

Dec 12, 2025

I went back to check the numbers, what I have is:

I am not sure if SMIC N+2 density was ever released or calculated?

Dec 12, 2025

I think this characterization by TechInsights is off. The author provided me some key details. I posted only a rough version on X...

Dec 12, 2025

While SMIC’s N+3 process shows meaningful density improvements, our comparative measurements confirm it remains significantly less...

Dec 12, 2025

TechInsights has completed an exploratory teardown and process analysis of the Huawei Kirin 9030 application processor used in the new...

Dec 12, 2025

Great response -- and very interesting re: materials. That sounds like a supply chain weakspot, at least when you did the analysis...

Dec 12, 2025

Other than HBM they are similar. but the Chip designs are different so its a wafer start issue (Assume cycle time from start to package...

Dec 12, 2025

F

Yeah, I remembered the gate pitch had been "abnormally" large, but actually it's just that SMIC density < Samsung density < TSMC density...

Dec 12, 2025

CAMPBELL, Calif. – December 11, 2025 – Arteris, Inc. (Nasdaq: AIP), a leading provider of system IP for accelerating semiconductor...

Dec 12, 2025

F

N+2 is 93 mtr.

It has 63nm gate pitch and 252nm cell height which revealed by Techinsight.

118 mtr mean ~27% density improve, very huge.

Dec 12, 2025

Like.

TechInsights has completed an exploratory teardown and process analysis of the Huawei Kirin 9030 application processor used in the new...

Like.

TechInsights has completed an exploratory teardown and process analysis of the Huawei Kirin 9030 application processor used in the new... Xebec replied to the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm.Just a spot check, the Semiwiki article on TSMC N5, has: 171 MTr/mm2, but agrees with 51 and 57 gate pitches for N5 and N7...

Xebec replied to the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm.Just a spot check, the Semiwiki article on TSMC N5, has: 171 MTr/mm2, but agrees with 51 and 57 gate pitches for N5 and N7... Xebec reacted to Fred Chen's post in the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm with

Xebec reacted to Fred Chen's post in the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm with Like.

I went back to check the numbers, what I have is: I am not sure if SMIC N+2 density was ever released or calculated?

Like.

I went back to check the numbers, what I have is: I am not sure if SMIC N+2 density was ever released or calculated? Xebec reacted to Fred Chen's post in the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm with

Xebec reacted to Fred Chen's post in the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm with Like.

I think this characterization by TechInsights is off. The author provided me some key details. I posted only a rough version on X...

Like.

I think this characterization by TechInsights is off. The author provided me some key details. I posted only a rough version on X... Xebec reacted to KevinK's post in the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm with

Xebec reacted to KevinK's post in the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm with Like.

While SMIC’s N+3 process shows meaningful density improvements, our comparative measurements confirm it remains significantly less...

Like.

While SMIC’s N+3 process shows meaningful density improvements, our comparative measurements confirm it remains significantly less... Xebec reacted to Fred Chen's post in the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm with

Xebec reacted to Fred Chen's post in the thread SMIC N+3 Confirmed: Kirin 9030 Analysis Reveals How Close SMIC Is to 5nm with Like.

TechInsights has completed an exploratory teardown and process analysis of the Huawei Kirin 9030 application processor used in the new...

Like.

TechInsights has completed an exploratory teardown and process analysis of the Huawei Kirin 9030 application processor used in the new... Xebec replied to the thread How "fungible" are memory maker fabs for switching between memory types?.Great response -- and very interesting re: materials. That sounds like a supply chain weakspot, at least when you did the analysis...

Xebec replied to the thread How "fungible" are memory maker fabs for switching between memory types?.Great response -- and very interesting re: materials. That sounds like a supply chain weakspot, at least when you did the analysis... Xebec reacted to MKWVentures's post in the thread How "fungible" are memory maker fabs for switching between memory types? with

Xebec reacted to MKWVentures's post in the thread How "fungible" are memory maker fabs for switching between memory types? with Like.

Other than HBM they are similar. but the Chip designs are different so its a wafer start issue (Assume cycle time from start to package...

Like.

Other than HBM they are similar. but the Chip designs are different so its a wafer start issue (Assume cycle time from start to package... AmandaK posted the thread Arteris to Expand Portfolio with Acquisition of Cycuity, a Leader in Semiconductor Cybersecurity Assurance in Arteris.CAMPBELL, Calif. – December 11, 2025 – Arteris, Inc. (Nasdaq: AIP), a leading provider of system IP for accelerating semiconductor...

AmandaK posted the thread Arteris to Expand Portfolio with Acquisition of Cycuity, a Leader in Semiconductor Cybersecurity Assurance in Arteris.CAMPBELL, Calif. – December 11, 2025 – Arteris, Inc. (Nasdaq: AIP), a leading provider of system IP for accelerating semiconductor... Like.

N+2 is 93 mtr. It has 63nm gate pitch and 252nm cell height which revealed by Techinsight. 118 mtr mean ~27% density improve, very huge.

Like.

N+2 is 93 mtr. It has 63nm gate pitch and 252nm cell height which revealed by Techinsight. 118 mtr mean ~27% density improve, very huge.