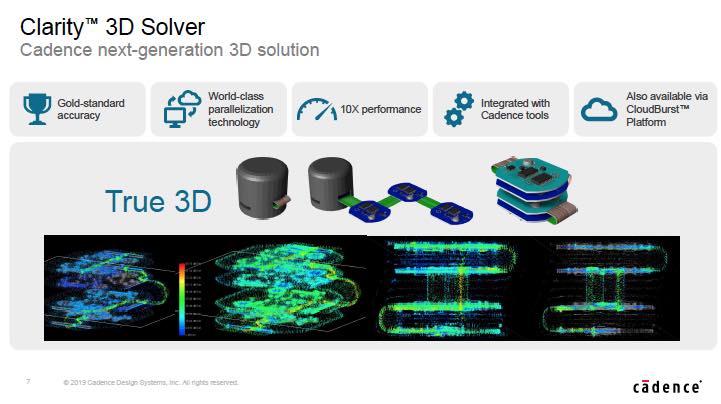

The need for full wave EM solvers has been creeping into digital design for some time. Higher operating frequencies – like those found in 112G links, lower noise margins – caused by multi level signaling such as in PAM-4, and increasing design complexity – as seen in RDL structures, interposers, advanced connector… Read More

Tag: solver

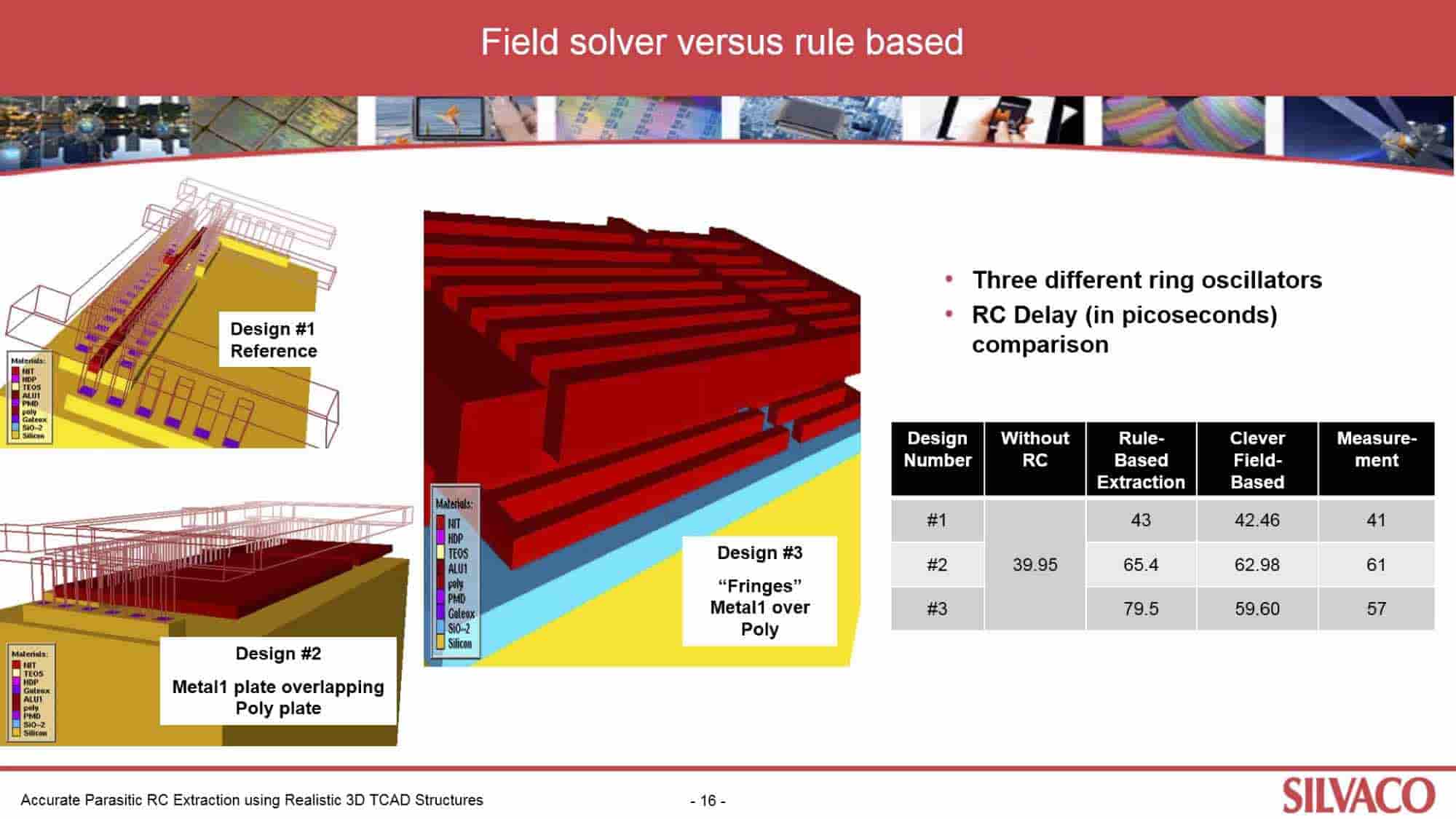

Sometimes a Solver is a Suitable Solution

Traditional, rule based, RC extractors rely on a substantial base of assumptions, which are increasingly proving unreliable. Having accurate RC extraction results for parasitic R’s and C’s is extremely important for ensuring proper circuit operation and for optimizing performance and power. Advanced process nodes are making… Read More

Design units come to faster Riviera-PRO release

For the latest incremental improvements to its Riviera-PRO functional verification platform, Aldec has turned to streamlining random constraint performance. The new Riviera-PRO 2016.02 release also is now fully supported on Windows 10 and adds a new debugger tool.… Read More

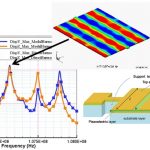

Coventor Brings More Accuracy & Performance into Design of MEMS Devices

Although MEMS devices in various forms are now found in most electronic devices, predominantly in mobile, automotive, aerospace and many other applications, their major revolution, I believe, is yet to happen. We are seeing rapid innovation in MEMS reflected by their improvements in precision, performance, size reduction,… Read More

Xilinx & Apache Team up for FPGA Reliability at 20nm

In this age of SoCs with hundreds of IPs from different sources integrated together and working at high operating frequencies, FPGA designers are hard pressed keeping up the chip reliability from issues arising out of excessive static & dynamic IR drop, power & ground noise, electro migration and so on. While the IPs are… Read More