I’ve read about MoSys over the years and had the chance this week to interview Nani Subraminian, Engineering Manager about the types of EDA tools that they use and how design data management has been deployed to keep the design process organized. My background includes both DRAM and SRAM design, so I’ve been curious… Read More

Tag: mentor

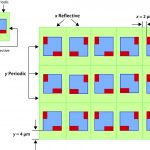

Advanced Memory Cell Characterization with Calibre xACT 3D

Advanced process technologies for manufacturing computer chips enable more functionality, higher performance, and low power through smaller sizes. Memory bits on a chip are predicted to double every two years to keep up with the demand for increased performance.

To meet these new requirements for performance and power, memory… Read More

Imera Virtual Fabric

Virtual fabric sounds like something that would be good for making the emperor’s new clothes. I talked today to Les Spruiell of Imera to find out what it really is.

Anyone who has worked as either a designer or as an EDA engineer has had the problem of a customer who has a problem but can’t send you the design since it is (a)… Read More

Learning Verilog for ASIC and FPGA Design

Verilog History

Prabhu Goel founded Gateway Design Automation and Phil Moorby wrote the Verilog language back in 1984. In 1989 Cadence acquired Gateway and Verilog grew into a de-facto HDL standard. I first met Prabu at Wang Labs in 1982 where I designed a rather untestable custom chip named the WL-2001 (yes, it was named to honor… Read More

AMS Design at AnSem

AnSem has been in the AMS design business since 1998 and uses a variety of commercial EDA tools along with internally developed tools and scripts to automate the process of analog design and technology porting. Their IC designers have completed some 40 AMS projects in diverse areas like:

- RF CMOS

- LNA, VCO, Mixers

- Synthesizers

- Low-IF/Zero-IF

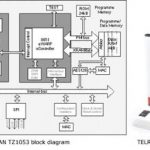

How ST-Ericsson Improved DFM Closure using SmartFill

DFM closure is a growing issue these days even at the 45nm node, and IC designers at ST-Ericsson have learned that transitioning from dummy fill to SmartFill has saved them time and improved their DFM score.

The SOC

ST-Ericsson designed an SOC for mobile platforms called the U8500 and their foundry choice was a 45nm node at STMicroelectronics… Read More

Circuit Simulation and Ultra low-power IC Design at Toumaz

I read about how Toumaz used the Analog Fast SPICE (AFS) tool from BDA and it sounded interesting so I setup a Skype call with Alan Wong in the UK last month to find out how they design their ultra low-power IC chips.

Interview

Q: Tell me about your IC design background.

A: I’ve been at Toumaz almost 8 years now and before that at Sony… Read More

A Verilog Simulator Comparison

Intro

Mentor, Cadence and Synopsys all offer Verilog simulators, however when was the last time that you benchmarked your simulator against a tool from a smaller company?

I just heard from an RTL designer (who wants to remain anonymous) about his experience comparing a Verilog simulator called CVC from Tachyon against ModelSim… Read More

Cadence ClosedAccess

There are various rumors around about Cadence starting to close up stuff that has been open for a long time. Way back in the midst of time, as part of the acquisition of CCT, the Federal Trade Commission forced Cadence to open up LEF/DEF and allow interoperability of Cadence tools (actually only place and route) I believe for 10 years.… Read More

I love you, you love me, we’re a happy family…

The CEO panel at the 2nd GTC wasn’t especially enlightening. The theme was that going forward will require cooperation for success and everyone was really ready to cooperate.

The most interesting concept was Aart talking about moving from what he called “scale complexity” aka Moore’s law to what he … Read More