The transition to the digital age from a mostly analog world really began with the invention of the A-to-D and D-to-A converters. However scalar processors can easily be overwhelmed by the copious data produced by something as simple as an audio stream. To solve this problem and to really jumpstart the digital age, the development of the digital signal processor (DSP) catalyzed the sweeping changes we are still witnessing today. If you are old enough, you probably remember when early DSPs were added to audio systems to enhance sound. Because of their immense usefulness, the applications of DSPs have expanded to include an ever-growing list of domains. However, it is a safe generalization to say that they’re more most useful in helping computing systems deal with the external world.

With applications as diverse as RF signal processing, automotive sensor RADAR, LIDAR, sensor fusion, vision, and in some cases machine learning, DSPs have needed to support a wider range of operations and increasing parallelism. To help SoC designers meet these challenges Synopsys has just introduced the impressive ARC VPX family of DSP Processor IP. The two new entrants in this family are the VPX5 and a Functional Safety version called the VPX5FS. So, what makes these DSPs different?

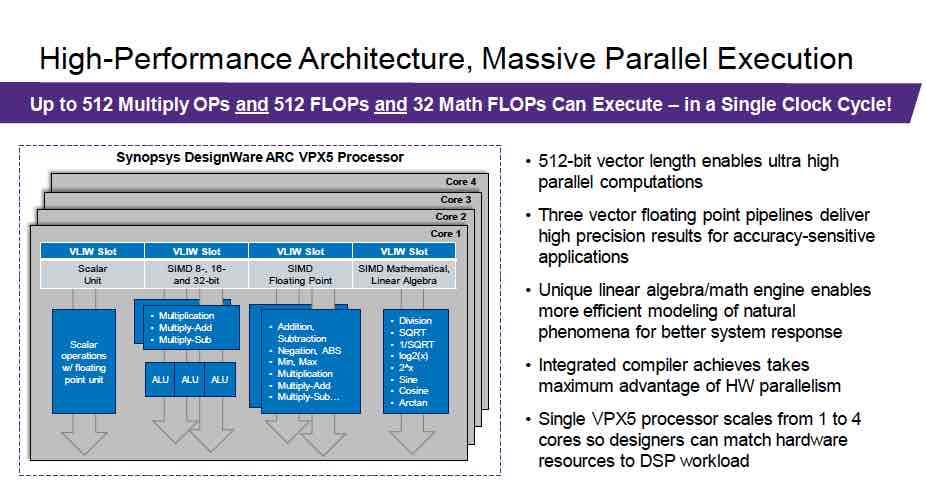

The answer in a word is parallelism at every level. Each VPX core offers 4 VLIW execution slots. VLIW introduces parallelism with the ability to encode multiple instructions for parallel execution in the same process or cycle. VLIW can be tricky to program because intermediate results in long expressions need to be cascaded through multiple VLIW operations. However, Synopsys has announced ARC MetaWare Tools that hide the mechanics of VLIW operation from developers, so they can write C++ code as usual and reap the benefits of VLIW acceleration.

The next level of parallelism for the VPX DSP IP cores is support for SIMD. SIMD lets one instruction operate on many (up to 512 for VPX5) data items. Three of the VLIW slots support SIMD, providing massive acceleration. Once again, Synopsys has made sure that the ARC MetaWare Tools help software developers easily take advantage of SIMD with minimal effort.

On top of this, VPX can scale up to 4 cores, adding a third layer of parallelism in VPX based SoCs. This ‘three dimensional’ parallelism gives the VPX based SoCs the ability to tackle a range of problems far beyond the now seemingly quaint uses for the first generations of DSPs.

A trend in machine learning, where parallel processing pays off, is the to move toward 8 or 16 bit integer operations to speed ML recognition algorithms. However, the real world is a messy place filled with data that can only be characterized by floating point values. Before a ML algorithm can be applied, high quality sensor data is needed, often in the form of sensor fusion output, to properly characterize what is happening in the real world. Floating point data offers high dynamic range and higher accuracy than integer values. The VPX cores support floating point operations in their VLIW slots. To further help with processing, VPX offers a linear algebra math unit that can perform sine, cosine, arctan, sqrt, log, exponent and other operations. Of course, there is also a VLIW slot that can use SIMD on 8, 16 and 32 bit integer data.

In their announcement Synopsys highlights several key areas where they see the VPX DSPs playing an important role. They are LIDAR, RADAR, Sensor Fusion and 5G communications. The low power and configurability of the VPX cores mean that they can be applied where needed to help process enormous amounts of data. A result of having higher performance in the system is a potential reduction of sensors and sensor complexity. For 5G, where signal processing becomes more important because of channel complexity, additional processing power can help improve data rates and reduce power. The full announcement with more details on the VPX5 and VPX5FS can be found on the Synopsys website.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.