Once upon a time there was a struggle for verification completion of semiconductor designs at gate level. Today, beyond imagination, there is a struggle to verify a design with billions of gates at the RTL level which may never complete. The designs are large SoCs with complex architectures and several constraints of area, performance,… Read More

Semidynamics Shakes Up Embedded World 2024 with All-In-One AI IP to Power Nextgen AI ChipsSemidynamics takes a non-traditional approach to design enablement.…Read More

Semidynamics Shakes Up Embedded World 2024 with All-In-One AI IP to Power Nextgen AI ChipsSemidynamics takes a non-traditional approach to design enablement.…Read More Silicon Catalyst partners with Arm to launch the Arm Flexible Access for Startups Contest!Winner and Runner-up to receive the contest’s largest…Read More

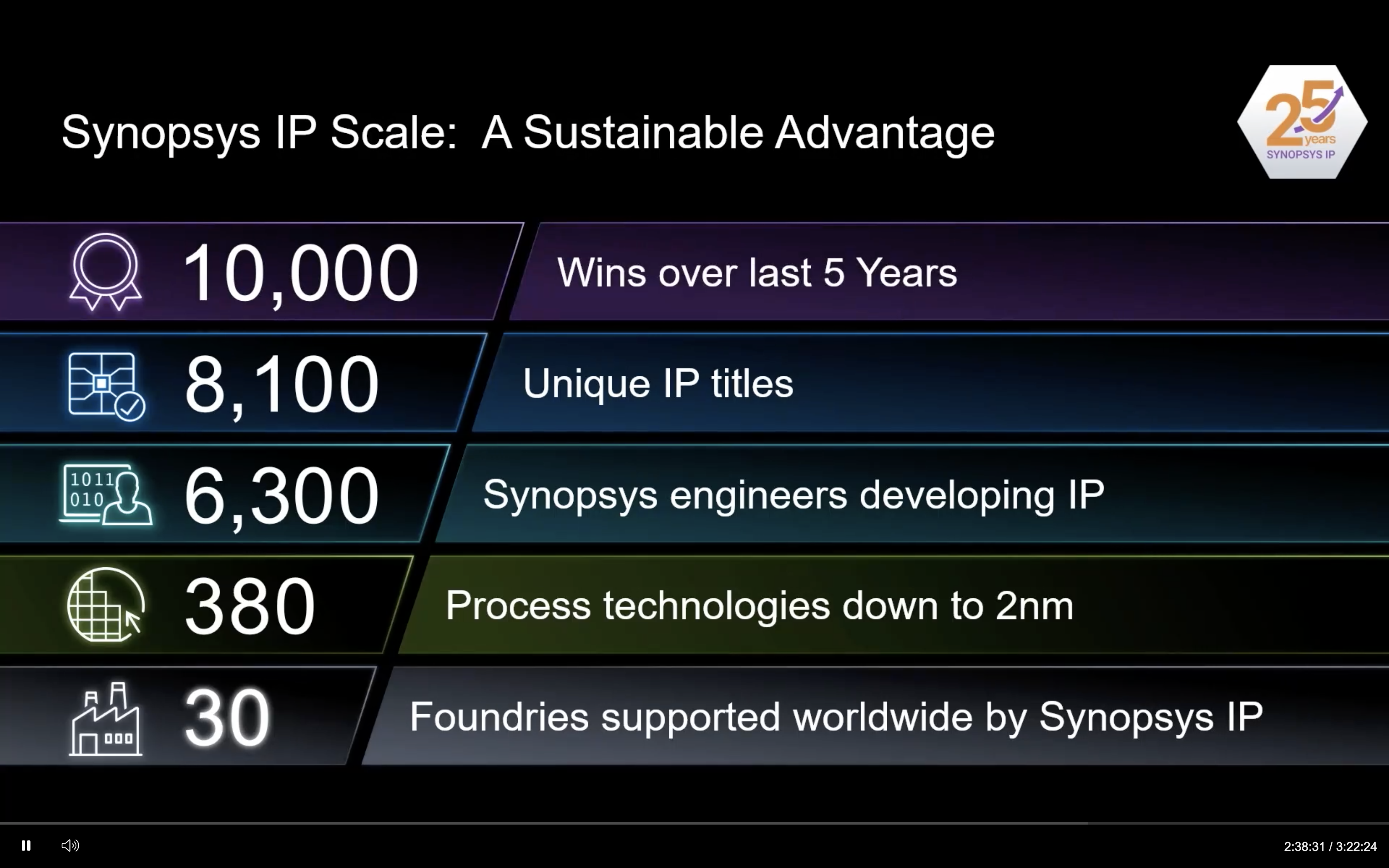

Silicon Catalyst partners with Arm to launch the Arm Flexible Access for Startups Contest!Winner and Runner-up to receive the contest’s largest…Read More Synopsys Design IP for Modern SoCs and Multi-Die SystemsSemiconductor intellectual property (IP) plays a critical role…Read More

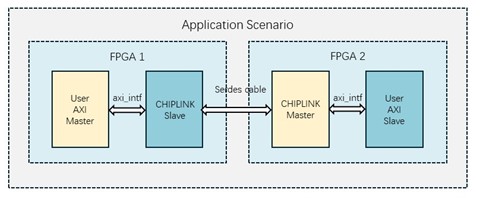

Synopsys Design IP for Modern SoCs and Multi-Die SystemsSemiconductor intellectual property (IP) plays a critical role…Read More Enhancing the RISC-V Ecosystem with S2C Prototyping SolutionRISC-V's popularity stems from its open-source framework, enabling…Read More

Enhancing the RISC-V Ecosystem with S2C Prototyping SolutionRISC-V's popularity stems from its open-source framework, enabling…Read MoreFD-SOI: 20nm Performance at 28nm Cost

There has been a lot of controversy about whether FD-SOI is or is not cheaper to manufacture than FinFET. Since right now FinFET is a 16nm process (22nm for Intel) and FD-SOI is, for now, a 28nm process it is not entirely clear how useful a comparison this is. Scotten Jones has very detailed process cost modeling software (that is what… Read More

A Win-Win Royalty Deal Structure in IP Business

Royalty is a critical component in any IP deal. SoC companies want IP companies to share the risk of success (or failure) of their SoC and to enable that they want IP vendors to accept a substantial part of their payment to be paid as royalty. But the customers are also not very interested to shell out huge money to IP companies if the SoC… Read More

Altera vs Xilinx FinFET Update

One of the things I do in my spare time is listen to quarterly conference calls and try to sort fact from fiction. I compare past calls to the current one and attempt to predict what’s coming next. Confucius said, “Study the past if you would define the future” and I’m a big believer in that.

Paul McLellan wrote about the Xilinx call earlier… Read More

Getting a Tapeout Quote in 10 Minutes!

On Thursday, July 31[SUP]st[/SUP] at 8 AM Pacific Daylight Time I’ll be moderating a webinar that will demo eSilicon’s new GDSII quoting portal. You can find more details about the webinar here, and you can register here.

I’ve worked with a lot of companies that do advanced custom IC designs. Getting a quote that covers all the NRE… Read More

Taking a leap forward from TCAD

We all know that Technology Computer Aided Design (TCAD) simulations are essential in developing processes for semiconductor manufacturing. From the very nature of these simulations (involving physical structure and corresponding electrical characteristics of a transistor or device), they are predominantly finite-element… Read More

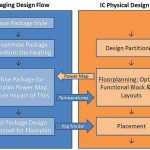

Temperature – The Fourth Aspect to Look at in SoC Design

In my career in semiconductor industry, I can recall, in the beginning there was emphasis on design completion with automation as fast as possible. The primary considerations were area and speed of completion of a semiconductor design. Today, with unprecedented increase in multiple functions on the same chip and density of the… Read More

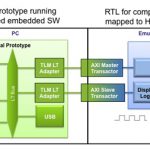

Hybrid Emulation

Hybrid emulation is when part of the system is run in the emulator and part of the system is run in a virtual prototype. Typically a model of the processor(s) is run in the virtual platform and then the rest of the design is modeled by running the RTL on the emulator. I talked to Tom Borgstrom at Synopsys about what technology they have … Read More

CEVA creating a wearable IP platform

Processor and GPU cores usually get the limelight, driven by the ARM and Imagination machines occupying the center square of most SoC designs. CEVA has quietly been assembling DSP IP in most of the squares around the edge, and may have just reached critical mass for wearables and IoT devices.… Read More

Clever IoT Devices are Coming!

Paul McLellan and I spent the evening with Samsung at the Bentley Reserve in San Francisco last night. One thing I discussed with them in great detail was IoT devices. Samsung is investing heavily in IoT and the supporting infrastructure. In fact, there is a rumor that Samsung is acquiring home automation company SmartThings for… Read More

ASML- Soft revenues & Orders – But…China 49% – Memory Improving