Tuesday was the Kaufman award dinner. This year it was awarded to Lucio Lanza. Last week I wrote about how Lucio ended up in EDA, although that was not where he finished up. He is currently a venture capitalist running Lanza Technology Ventures, one of the few VCs to make any investments in the EDA/IP/semiconductor space. Also, unlike… Read More

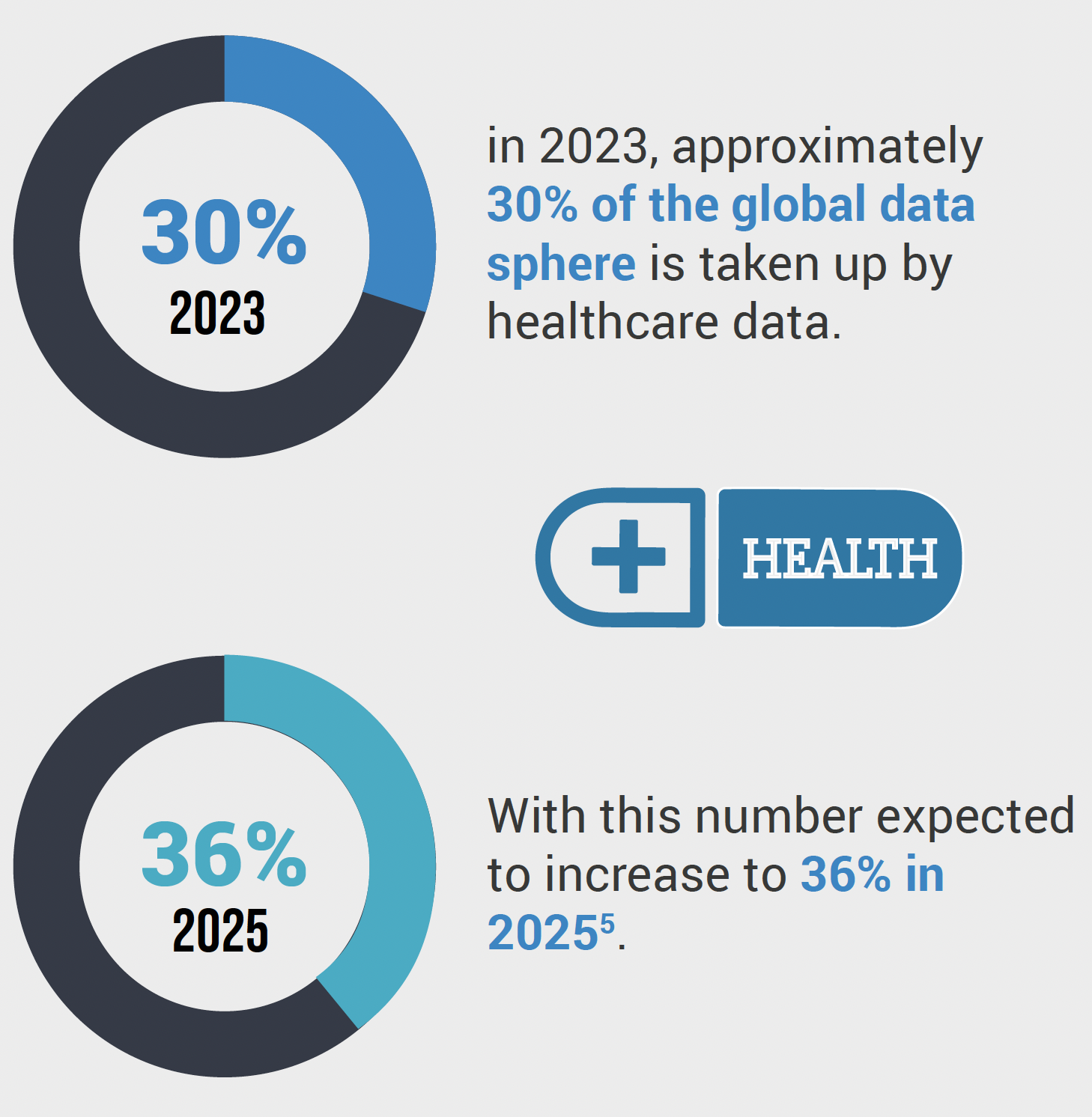

The Data Crisis is Unfolding – Are We Ready?The rapid advancement of technology, including generative AI,…Read More

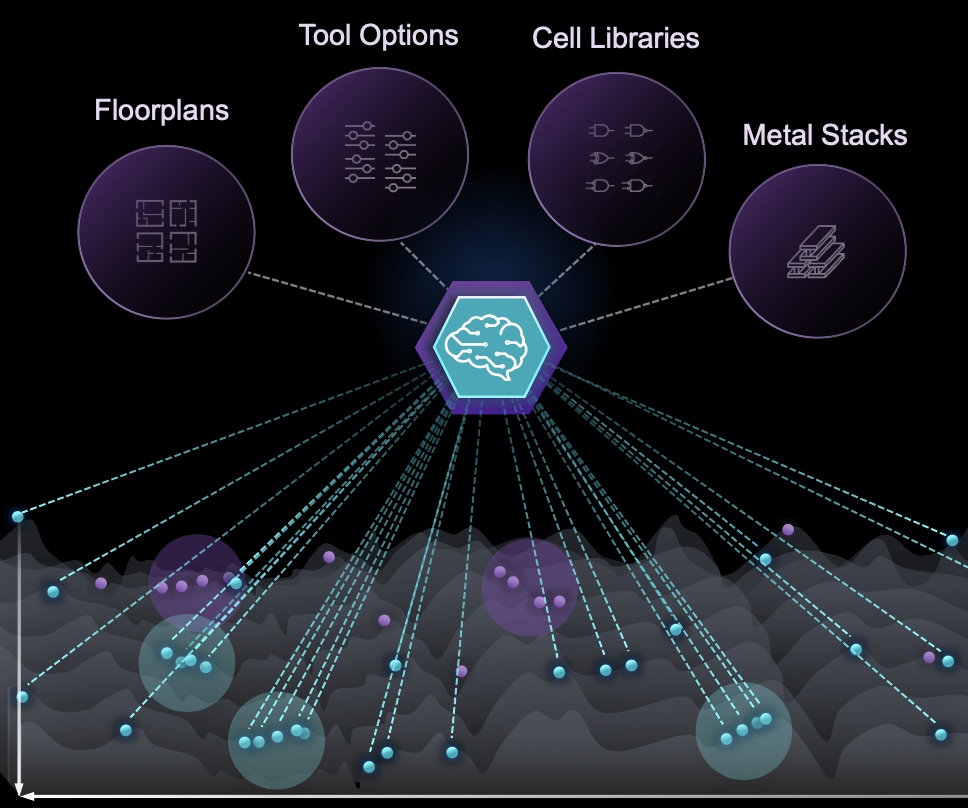

The Data Crisis is Unfolding – Are We Ready?The rapid advancement of technology, including generative AI,…Read More Synopsys Presents AI-Fueled Innovation at SNUG 2024SNUG is the premier event for Synopsys to…Read More

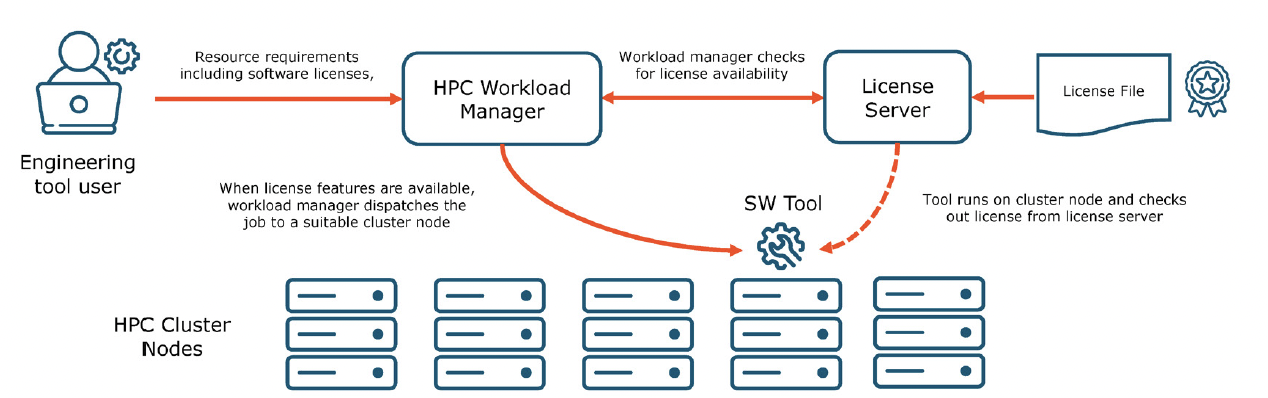

Synopsys Presents AI-Fueled Innovation at SNUG 2024SNUG is the premier event for Synopsys to…Read More Navigating the Complexities of Software Asset Management in Modern EnterprisesIn today's digital age, software has become the…Read More

Navigating the Complexities of Software Asset Management in Modern EnterprisesIn today's digital age, software has become the…Read MoreSemiconductor Safety

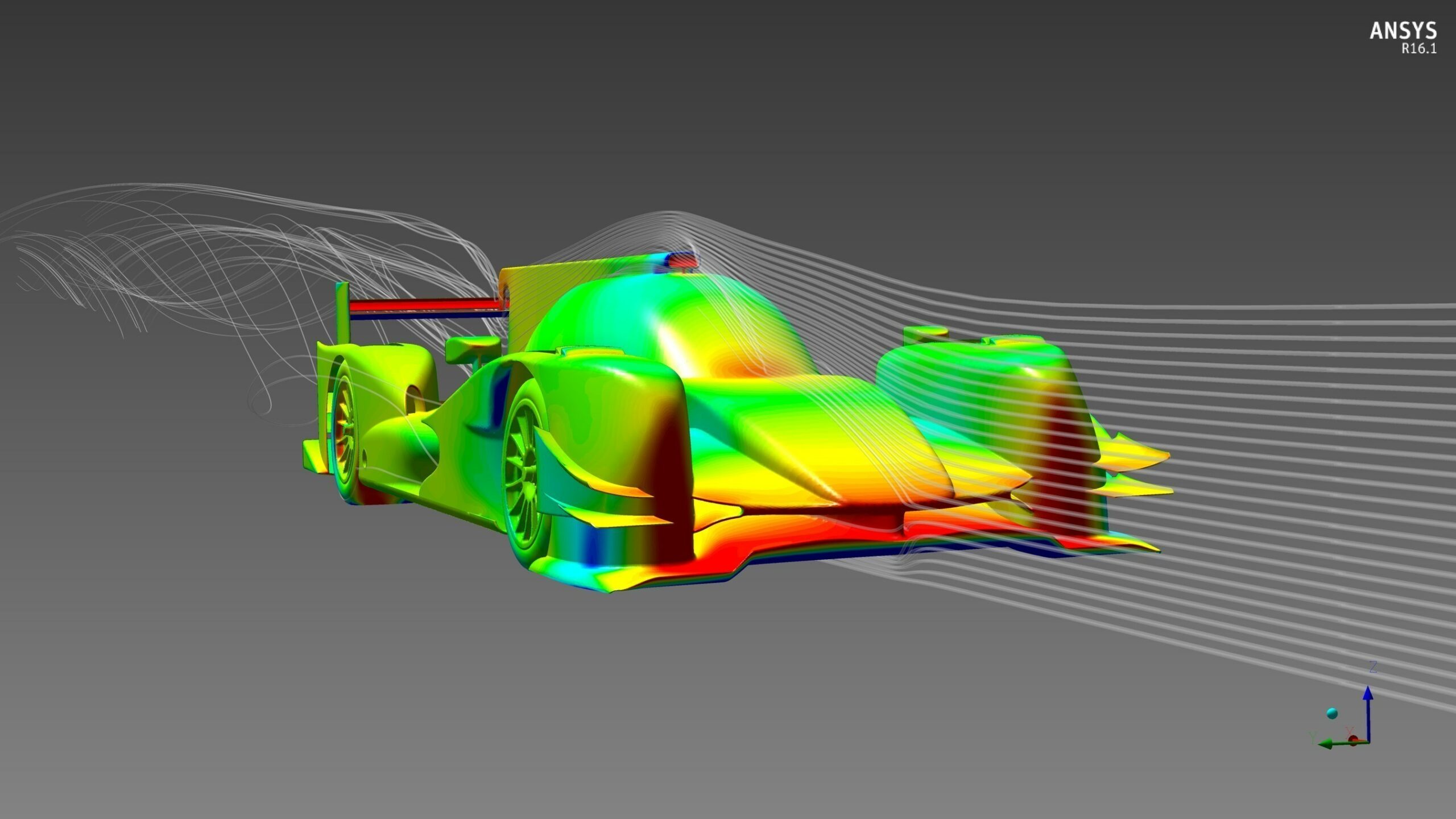

Semiconductors and automotive are now like peanut butter and jelly. Certainly you can have one without the other but why would you? I remember when a car first talked to me telling me that the door was ajar. It sounded more like, “the door is a jar” but I got the point. Now my car tells me just about everything including what is wrong with… Read More

Daylight Savings Time and the IoT

On Sunday in the USA we changed our clocks back one hour to account for Daylight Savings Time and I was reminded of how far we have to go in getting all of our devices to understand and automatically account for the time. Despite all of the talk about IoT and how it has the promise to automate our lives, we still have to manually set the time.… Read More

MQTT not IoT “god protocol”, but getting closer

One protocol, and its descendants, drove the success of the World Wide Web. IP, or Internet Protocol, is the basis of every browser connection and the backbone of IT data centers. Some assumed that the Internet of Things would follow suit,… Read More

Samsung 14nm is the one delayed!

As you may have read, the CEO of Ultratech made some unfortunate statements on the recent quarterly conference call in regards to FinFET Yield. As a result there has been a lot of speculation about the who, what, and why. I blogged about it because it interested me personally plus I wanted to collect more data on the subject. Some of … Read More

FD-SOI, an Opportunity for China?

Last month in Shanghai was a meeting of the FD-SOI consortium. The focus of the meeting was largely on the suitability of using FD-SOI to serve the Chinese market. The fabs in China are not right on the bleeding edge and are very cost-sensitive so 28nm is probably as advanced as they will get for a long time if not indefinitely. China … Read More

In-Design DFM Signoff for 14nm FinFET Designs

While FinFET yield controversy is going on, I see a lot being done to improve that yield by various means. One prime trend today, it must be, it’s worthwhile, is to pull up various signoffs as early as possible during the design cycle. And DFM signoff is a must with respect to yield of fabrication. This reminds me about my patents filed… Read More

Its a bouncing baby IEEE standard!

Pass the cigars! On November 3rd, 2014, the IEEE-SA Standards Board finally approved IEEE P1687 as a new standard. From now on, you can drop the “P” and just call it 1687, or to its friends, IJTAG. Now would be a good time to sign up for an IJTAG technical workshop.

The new IEEE 1687 Internal JTAG (IJTAG) standard is changing… Read More

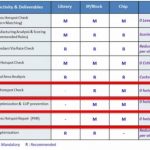

Improve Test Robustness & Coverage Early in Design

In a semiconductor design, keeping the design testable with high test coverage has always been a requirement. However with shrinking technology nodes and large, dense SoC designs and complex logic structures, while it has become mandatory to reach close to 100% test coverage, it’s extremely difficult to cope with the explosion… Read More

Let the FinFET Yield Controversy Begin!

It never ceases to amaze me how people point fingers and create controversy to cover their mistakes. It happened at 40nm, 28nm, and again at 20nm and now it is time for the regularly scheduled yield controversy. Of course any conversation about semiconductor yield generates clicks for SemiWiki so I’m happy to play along.

It generally… Read More

The Data Crisis is Unfolding – Are We Ready?