jms_embedded

Active member

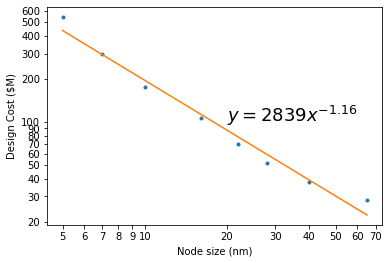

Handel Jones at IBS was cited in this 2018 article Big Trouble at 3nm with the following graph of skyrocketing design costs.

I graphed these numbers on a log-log plot and did a linear fit:

Does anyone have a sense of whether the assumption is for constant die area (more transistors at advanced nodes) or constant transistor count (die shrinks) --- I'm guessing it's the former. If someone's doing a die shrink from node N to node N+1, does the design cost increase much?

I graphed these numbers on a log-log plot and did a linear fit:

Does anyone have a sense of whether the assumption is for constant die area (more transistors at advanced nodes) or constant transistor count (die shrinks) --- I'm guessing it's the former. If someone's doing a die shrink from node N to node N+1, does the design cost increase much?