- This event has passed.

Webinar: Power Integrity Challenges and Solutions for Interposer Design

May 17, 2023 @ 11:00 AM - 12:00 PM

Join us on May 17 for the latest 3D-IC webinar series, “Power Integrity Challenges and Solutions for Interposer Design.” The discussion will focus on interposer power analysis as an isolated case and in context with the dice instantiated in a 3D-IC device. The presentation will then explore the completed multi-chip design in a system simulation.

TIME:

MAY 17, 2023

11 AM EDT

Venue:

Virtual

About this Webinar

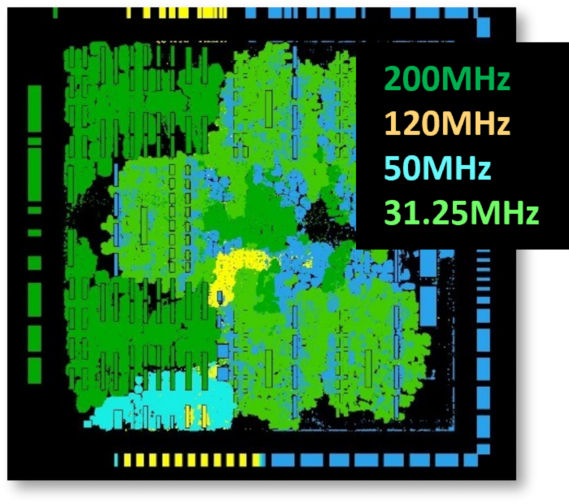

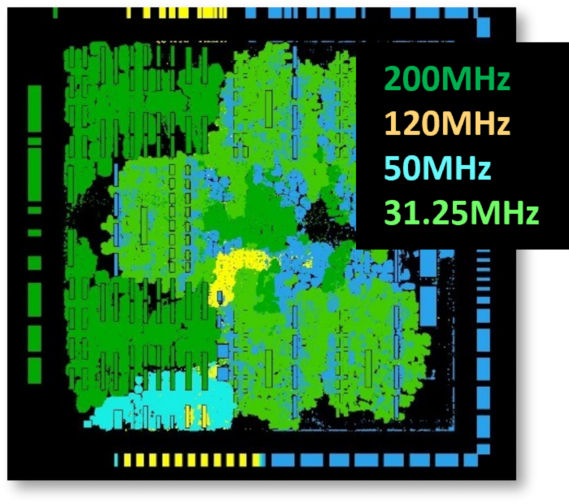

The trend in chiplet packaging designs is increased density connections to the dies through micro-bumps or even more dense hybrid bonding. This has introduced larger current densities and variations into the power supply network than seen with a single die packaging.

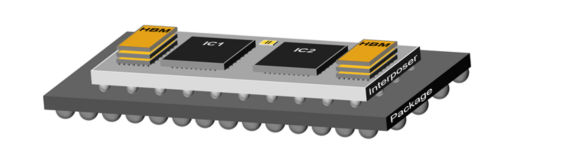

It’s common to use an interposer as the interface between the package and the chiplets. The interposer must be able to supply power to each of the chiplets so that the system of dies functions correctly. This webinar will analyze interposers’ power integrity in the context of the system of dies they support.

What You Will Learn

- How to analyze the power grid of an interposer as a stand-alone die

- How to analyze an interposer in the context of the system of dies it supports

- How to create a macro model of the interposer that can be used for system level analysis

Who Should Attend

Semiconductor and electronics engineers involved in 3D-IC design

Speakers

Chris Ortiz is a senior principal application engineer at ANSYS. His interests include chip-level modeling for system-level power, signal, and thermal integrity. He has been in the semiconductor industry for over 20 years and received his Ph.D. in physics from the University of Notre Dame.

The Data Crisis is Unfolding – Are We Ready?